基于PCB 仿真的高速时钟电路设计研究

2013-03-29

张艳丽 安琪 王砚方

23

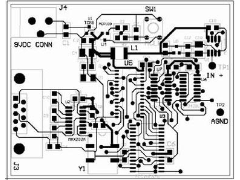

1 引言 在目前正进行的北京正负电子对撞机二期升级改造工程(BECPII) 中,北京谱仪(BESIII) 的飞行时间(Time of Flight ,简称:TOF) 读出电子学需要对一种具有25ps 分辨率的数据驱动型时间测量器件- HPTDC(High Performance TDC) 进行性能测试。为此,我们设计了一种具有更高精度的专用高精度信号发生器。由于时钟电路是整个高 ..

[查看全文]

PCB Layout爬电距离、电气间隙的确定

2013-03-29

28

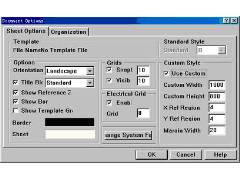

爬电距离的确定:首先需要确定绝缘的种类: 基本绝缘:一次电路与保护地 工作绝缘 ① :一次电路内部;二次电路内部 工作绝缘 ② :输入部分(输入继电器之前)内部,二次电路与保护地 加强绝缘:一次电路与二次电路;输入部分与一次电路;充电板输出与内部线路 再查看线路,确定线路之间的电压差 最后,从下表中查出对应的爬电 ..

[查看全文]

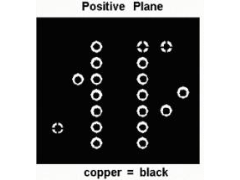

PCB线路板抄板方法及步骤

2013-03-28

12

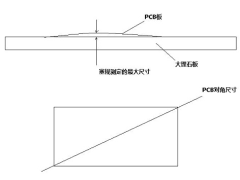

第一步,拿到一块PCB,首先在纸上记录好所有元气件的型号,参数,以及位置,尤其是二极管,三机管的方向,IC缺口的方向。最好用数码相机拍两张元气件位置的照片。 第二步,拆掉所有器件,并且将PAD孔里的锡去掉。用酒精将PCB清洗干净,然后放入扫描仪内,扫描仪扫描的时候需要稍调高一些扫描的像素,以便得到较清晰的图像, ..

[查看全文]

高速PCB设计指南(三)

2013-03-27

155

第一篇改进电路设计规程提高可测试性随着微型化程度不断提高,元件和布线技术也取得巨大发展,例如BGA外壳封装的高集成度的微型IC,以及导体之间的绝缘间距缩小到0.5mm,这些仅是其中的两个例子。电子元件的布线设计方式,对以后制作流程中的测试能否很好进行,影响越来越大。下面介绍几种重要规则及实用提示。通过遵守一 ..

[查看全文]

高速PCB镜像层设计

2013-03-25

张海龙

66

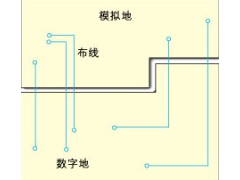

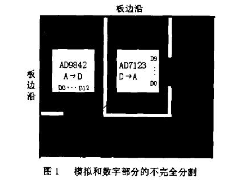

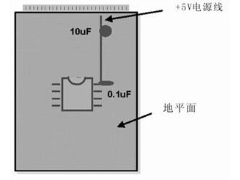

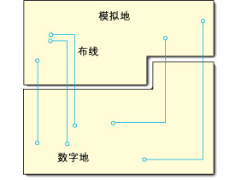

摘要:在高速多层PCB上, 镜像层在噪声控制方面起着重要作用。良好的镜像层设计可以降低杂散电感引起的噪声,有助于控制串扰、反射和电磁干扰。本文结合作者的实际设计重点探讨了局部接地层的应用,并通过一个数模混合电路实例给出了一种镜像层分割法以及一些实践中需要注意的问题。 现在的高速电路系统大多采用多层板, 而且 ..

[查看全文]

关于线宽与过孔铺铜的一点经验

2013-03-24

18

我先讲讲一点点布线常识(都是我的辛苦积累下来的呀,不是转发的),后面会讲一下实际中遇到的情况,请各位看客耐心看完。 我们在画PCB时一般都有一个常识,即走大电流的地方用粗线(比如50mil,甚至以上),小电流的信号可以用细线(比如10mil)。对于某些机电控制系统来说,有时候走线里流过的瞬间电流能够达到100A以上, ..

[查看全文]

高速PCB中的信号回流及跨分割

2013-03-24

张进东

14

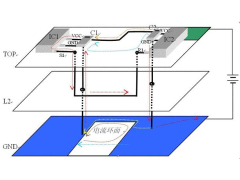

下面是我对电源回流的理解,跟大家分享一下^_^(其中介绍的一些处理方法在国内外很多高速PCB电路里都有应用的) 这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便作图,把层间距放大。 IC1为信号输出端,IC2为信号输入端(为简化PCB模型,假定接收端内含下接电阻)第三层为 ..

[查看全文]

PCB中有多个完全相同的电路块时简单设计方法

2013-03-23

12

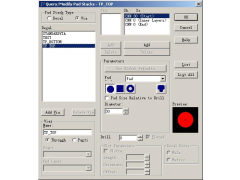

PCB中有多个完全相同的电路块时,先在sch中将电路块画成层次电路图的形式,更新到pcb中,就会产生多个room块,先将其中一个room的元件摆好位,布好内部连线,再选design->rooms->copy room formats,点击刚才布好的room,再随便点击其他room,就会弹出如下对话框,在这个对话框中可选copy元件及序号的摆放位置、 序 ..

[查看全文]

PCB布线设计(二)

2013-03-23

45

工程领域中的数字设计人员和数字电路板设计专家在不断增加,这反映了行业的发展趋势。尽管对数字设计的重视带来了电子产品的重大发展,但仍然存在,而且还会一直存在一部分与模拟或现实环境接口的电路设计。模拟和数字领域的布线策略有一些类似之处,但要获得更好的结果时,由于其布线策略不同,简单电路布线设计就不再是最 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 60

-

高速PCB设计指南(三)2013年03月27日 155

-

PCB布线设计(二)2013年03月23日 45

-

混合信号PCB的分区设计2013年03月04日 31

-

高速PCB设计指南(六)2012年12月29日 32

-

PCB布线设计(一)2012年10月22日 13

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 51

-

常用电阻,电容,电感标称值2024年11月22日 94

-

PSPICE 的应用2013年04月06日 38

-

Protel DXP的电路仿真设计2013年04月04日 22

-

Gerber转protel的方法2013年04月04日 32

-

在PADS中添加表面型测试点2013年04月03日 57

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 385

-

Protel dxp等长走线2013年01月02日 333

-

Cadence 中添加工艺库文件步骤2013年01月16日 292

-

电气安全距离要求及分类2012年09月06日 276

-

Allegro铺铜的学习2012年12月05日 186

-

在ORCAD中整体修改网络名称2012年07月26日 177