如何实现高速时钟信号的差分布线?

2013-03-23

11

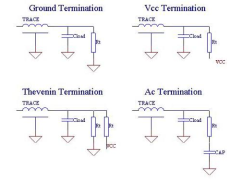

[提问] 在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线? [解答] 信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠 ..

[查看全文]

PCB设计指引(1)

2013-03-20

尹志宗

15

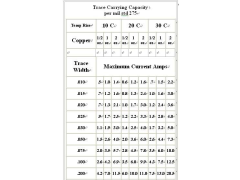

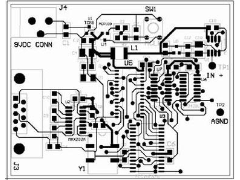

1. 目的和作用 1.1 规范设计作业,提高生产效率和改善产品的质量。 2. 适用范围 1.1 XXX公司开发部的VCD、超级VCD、DVD、音响等产品。 3. 责任 3.1 XXX开发部的所有电子工程师、技术员及电脑绘图员等。 4. 资历和培训 4.1 有电子技术基础; 4.2 有电脑基本操作常识; 4.3 熟悉利用电脑PCB绘图软件. 5. 工作指导(所有长度单位为MM ..

[查看全文]

SMT-PCB的设计原则

2013-03-19

11

一、SMT-PCB上元器件的布局 1、当电路板放到回流焊接炉的传送带上时﹐元器件的长轴应该与设备的传动方向垂直﹐这样可以防止在焊接过程中出现元器件在板上漂移或 “竖碑”的现象。 2、PCB 上的元器件要均匀分布﹐特别要把大功率的器件分散开﹐避免电路工作时PCB 上局部过热产生应力﹐影响焊点的可靠性。 3、双面贴 ..

[查看全文]

差分线对在高速PCB设计中的应用

2013-03-19

王延辉 谢锘

27

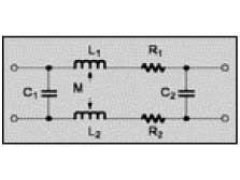

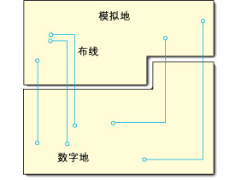

摘要:在高速数字电路设计过程中,工程师采取了各种措施来解决信号完整性问题,利用差分线传输高速数字信号的方法就是其中之一。在PCB中的差分线是耦合带状线或耦合微带线,信号在上面传输时是奇模传输方式,因此差分信号具有抗干扰性强,易匹配等优点。随着人们对数字电路的信息传输速率要求的提高,信号的差分传输方式必将 ..

[查看全文]

传输线阻抗计算和布线技巧

2013-03-18

16

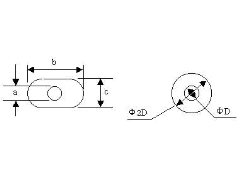

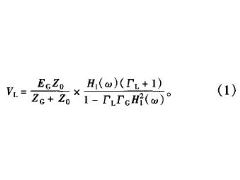

在高速逻辑电路或高频电路中,印刷电路板的布线对PCB的电磁兼容性(EMC)和电路的性能有重要影响。本文介绍电路板上传输线的阻抗计算公式、信号线的布局原则和传输导线的长度估计表。传输线阻抗计算公式 图1:传输导线模型如图1所示,设单线的电感为Li,互感为M,线间电容为Ci,则特征阻抗Zo=√(Leff/C),其中: Leff=L1 ..

[查看全文]

设计PCB时抗ESD 的方法

2013-03-18

于水

7

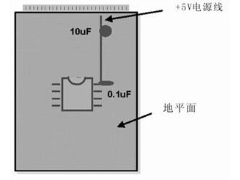

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁 MOSFET 和 CMOS 元器件的栅极;CMOS 器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(ESD)对电子设备的干扰和破坏,需要采取多种技术手段进 ..

[查看全文]

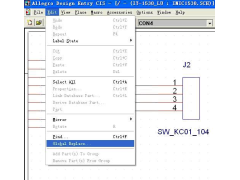

高速 PCB培训手记2(Allegro PCB SI的设计流程)

2013-03-17

宋宝华

14

Allegro PCB SI的设计流程包括如下六个步骤: Pre-Placement Solution Space Analysis Constraint-Driven Floorplanning Constraint-Driven Routing Post-Route DRC Post-Route Analysis Pre-Placement如图 9 所示先将芯片、接插件等按照设计要求预放置在板上。 图 9预放置 Database Setup Advisor 通过 Database Setu ..

[查看全文]

高速电路PCB设计技巧

2013-03-16

22

(一)、引言 电子技术的发展变化必然给板级设计带来许多新问题和新挑战。首先,由于高密度引脚及引脚尺寸日趋物理极限,导致低的布通率;其次,由于系统时钟频率的提高,引起的时序及信号完整性问题;第三,工程师希望能在PC平台上用更好的工具完成复杂的高性能的设计。由此,我们不难看出,PCB板设计有以下三种趋势: 高速数 ..

[查看全文]

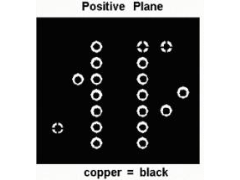

cadence 15.2PCB封装设计小结

2013-03-16

colin_li

17

在cadence15.2中设计PCB封装是在 PACKAGE DESIGNER中(如图)。 下面我通过设计TQFP100的例子将详细介绍Package Designer是如何设计PCB封装的。 以下是TQFP100 的封装信息: 下面介绍如何用Package Designer 设计PCB封装: 1、首先在alegro15.2中点击图标: ; 2、在出现的对话框中选择 Advanced Package Design ..

[查看全文]

BGA器件的PCB布局布线经验

2013-03-15

14

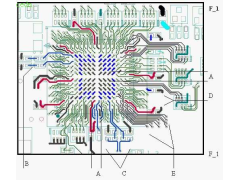

BGA是PCB上常用的组件,通常CPU、NORTH BRIDGE、SOUTH BRIDGE、AGP CHIP、CARD BUS CHIP…等,大多是以bga的型式包装,简言之,80﹪的高频信号及特殊信号将会由这类型的package内拉出。因此,如何处理BGA package的走线,对重要信号会有很大的影响。 通常环绕在BGA附近的小零件,依重要性为优先级可分为几 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 60

-

高速PCB设计指南(三)2013年03月27日 155

-

PCB布线设计(二)2013年03月23日 45

-

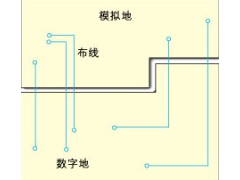

混合信号PCB的分区设计2013年03月04日 31

-

高速PCB设计指南(六)2012年12月29日 32

-

PCB布线设计(一)2012年10月22日 13

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 51

-

常用电阻,电容,电感标称值2024年11月22日 94

-

PSPICE 的应用2013年04月06日 38

-

Protel DXP的电路仿真设计2013年04月04日 22

-

Gerber转protel的方法2013年04月04日 32

-

在PADS中添加表面型测试点2013年04月03日 57

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 385

-

Protel dxp等长走线2013年01月02日 333

-

Cadence 中添加工艺库文件步骤2013年01月16日 292

-

电气安全距离要求及分类2012年09月06日 276

-

Allegro铺铜的学习2012年12月05日 186

-

在ORCAD中整体修改网络名称2012年07月26日 177