高速PCB板的电源布线设计

2013-01-14

金环衣 胡建萍 陈显萼

13

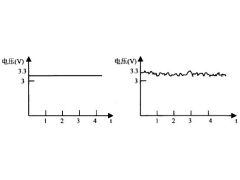

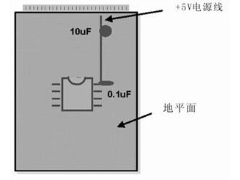

摘要:本文分析讨论了高速PCB板上由于高频信号的干扰和走线宽度的减小而产生的电源噪声和压降,并提出了高速PCB的电源模型,采用电源总线网络布线,选取合适的滤波电容,模拟数字地分开等几个简单有效的方法来解决高速PCB板的噪声和压降问题。 0 引言 随着集成电路工艺和集成度的不断提高,集成电路的工作电压越来越低,速度 ..

[查看全文]

高速PCB 设计中终端匹配电阻的放置

2013-01-13

17

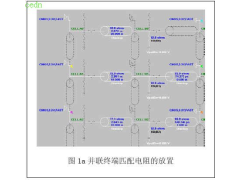

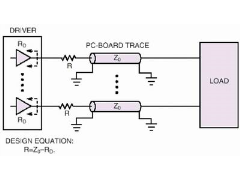

摘要:本文简要的总结了在高速数字设计中串联终端匹配和并联终端匹配的优缺点,并对这两种匹配方式的终端匹配电阻处于不同位置时的匹配效果做了相应的仿真和深入的分析,得出了串联终端匹配电阻对位置的要求没有终端匹配电阻严格这一结论,给出了一些关于终端匹配电阻摆放位置的建议。为在PCB 设计中如何放置终端匹配电阻提 ..

[查看全文]

PCB Layout指南

2013-01-13

24

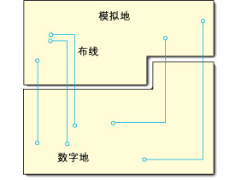

1. 一般规则 1.1 PCB板上预划分数字、模拟、DAA信号布线区域。 1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。 1.3 高速数字信号走线尽量短。 1.4 敏感模拟信号走线尽量短。 1.5 合理分配电源和地。 1.6 DGND、AGND、实地分开。 1.7 电源及临界信号走线使用宽线。 1.8 数字电路放置於并行总线/串行DTE接口 ..

[查看全文]

Cadence 高速PCB的时序分析(1)

2013-01-09

宋宝华

21

1.引言 时序分析,也许是SI 分析中难度最大的一部分。我怀着满腔的期许给Cadence 的资深工程师发了一封e-mail,希望能够得到一份时序分析的案例,但是希望化作了泡影。资深工程师告诉我,他们还没有能够编写一个具体的案例。于是,我不得不将我的期许转化为自己研究并编写一个具体的案例,与广大PCB 工程师共享,令大彼天下P ..

[查看全文]

高速PCB设计指南(七)

2013-01-07

24

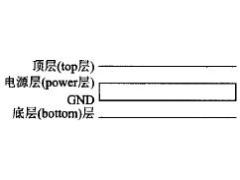

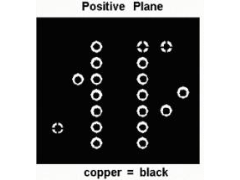

第一篇PCB基本概念1、“层(Layer) ”的概念与字处理或其它许多软件中为实现图、文、色彩等的嵌套与合成而引入的“层”的概念有所同,Protel的“层”不是虚拟的,而是印刷板材料本身实实在在的各铜箔层。现今,由于电子线路的元件密集安装。防干扰和布线等特殊要求,一些较新的电子产品中所用的印刷板不仅有上下两面供走线, ..

[查看全文]

PCB抗静电放电的措施

2013-01-06

12

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(ESD)对电子设备的干扰和破坏,需要采取多种技术手段进行 ..

[查看全文]

宽带数十MHz video增幅电路PCB的设计技巧

2013-01-02

12

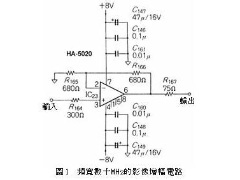

模拟信号尤其是类似0~数十MHz video信号宽带电路时,电路图上详细标示信号的流动路径与组件位置非常重要。图1 是电流复归型video 用OP 增幅器HA-5020 构成的影像增幅电路(video amplifier)。传统电压复归型OP增幅电路,gain一旦变大时频宽会降低,相较之下电流复归型OP增幅电路,由于理论上频宽取决于复归阻抗值决,因此不 ..

[查看全文]

DSP高速PCB抗干扰设计

2013-01-01

刘金锁

38

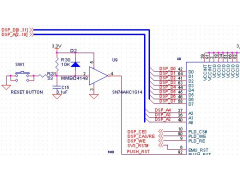

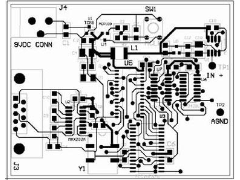

随着DSP(数字信号处理器)的广泛应用,基于DSP的高速信号处理PCB板的设计显得尤为重要。在一个DSP系统中,DSP微处理器的工作频率可高达数百MHz,其复位线、中断线和控制线、集成电路开关、高精度A/D转换电路,以及含有微弱模拟信号的电路都非常容易受到干扰;所以设计开发一个稳定的、可靠的DSP系统,抗干扰设计非常重 ..

[查看全文]

PCB设计方法和技巧(3)

2013-01-01

10

38、27M,SDRAM时钟线(80M-90M),这些时钟线二三次谐波刚好在VHF波段,从接收端高频窜入后干扰很大。除了缩短线长以外,还有那些好办法? 如果是三次谐波大,二次谐波小,可能因为信号占空比为50%,因为这种情况下,信号没有偶次谐波。这时需要修改一下信号占空比。 此外,对于如果是单向的时钟信号,一般采用源端串联 ..

[查看全文]

RF pcb design基本规则

2012-12-31

10

1.sirf reference典型的四,六层板,标准FR4材质 2.所有的元件尽可能的表贴 3.连接器的放置时,应尽量避免将噪音引入RF电路,尽量使用小的连接器,适当的接地 4.所有的RF器件应放置紧密,使连线最短和交叉最小(关键) 5.所有的pin有应严格按照reference schematic.所有IC电源脚应当有0.01uf的退藕电容,尽可能的离管脚近, ..

[查看全文]

高速PCB设计指南(六)

2012-12-29

32

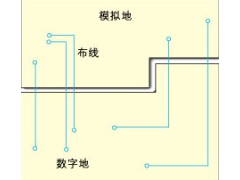

第一篇混合信号电路板的设计准则模拟电路的工作依赖连续变化的电流和电压。数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,它相当于判断逻辑状态的 “真”或“假”。在数字电路的高电平和低电平之间,存在“灰色”区域,在此区域数字电路有时表现出模拟效应,例如当从低电平向高电平(状态) ..

[查看全文]

Cadence 高速PCB的时序分析(2)

2012-12-27

16

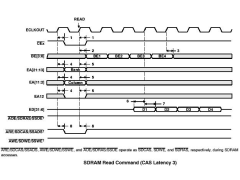

列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,我们将介绍什么是定时问题,怎样保证接收端的建立和保持时间。 信号经过传输线到达接收端之后,必须满足建立时间和保持时间这两个时序参数,它们由接收器本身的特性决定,可以 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 60

-

高速PCB设计指南(三)2013年03月27日 155

-

PCB布线设计(二)2013年03月23日 45

-

混合信号PCB的分区设计2013年03月04日 31

-

高速PCB设计指南(六)2012年12月29日 32

-

PCB布线设计(一)2012年10月22日 13

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 51

-

常用电阻,电容,电感标称值2024年11月22日 94

-

PSPICE 的应用2013年04月06日 38

-

Protel DXP的电路仿真设计2013年04月04日 22

-

Gerber转protel的方法2013年04月04日 32

-

在PADS中添加表面型测试点2013年04月03日 57

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 385

-

Protel dxp等长走线2013年01月02日 333

-

Cadence 中添加工艺库文件步骤2013年01月16日 292

-

电气安全距离要求及分类2012年09月06日 276

-

Allegro铺铜的学习2012年12月05日 186

-

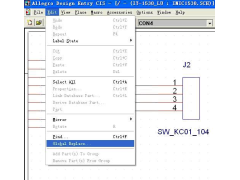

在ORCAD中整体修改网络名称2012年07月26日 177