PCB Layout指南

2013-01-13

24

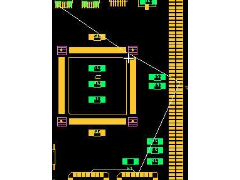

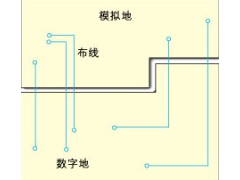

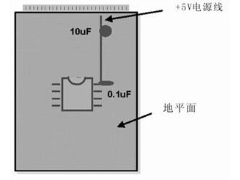

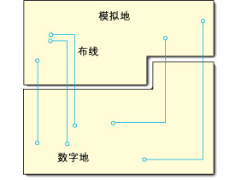

1. 一般规则 1.1 PCB板上预划分数字、模拟、DAA信号布线区域。 1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。 1.3 高速数字信号走线尽量短。 1.4 敏感模拟信号走线尽量短。 1.5 合理分配电源和地。 1.6 DGND、AGND、实地分开。 1.7 电源及临界信号走线使用宽线。 1.8 数字电路放置於并行总线/串行DTE接口 ..

[查看全文]

高速PCB 设计中终端匹配电阻的放置

2013-01-13

17

摘要:本文简要的总结了在高速数字设计中串联终端匹配和并联终端匹配的优缺点,并对这两种匹配方式的终端匹配电阻处于不同位置时的匹配效果做了相应的仿真和深入的分析,得出了串联终端匹配电阻对位置的要求没有终端匹配电阻严格这一结论,给出了一些关于终端匹配电阻摆放位置的建议。为在PCB 设计中如何放置终端匹配电阻提 ..

[查看全文]

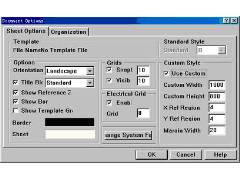

Protel DXP布线规则设置

2013-01-12

31

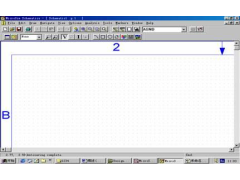

对于 PCB 的设计, Protel DXP 提供了详尽的 10 种不同的设计规则,这些设计规则则包括导线放置、导线布线方法、元件放置、布线规则、元件移动和信号完整性等规则。根据这些规则, Protel DXP 进行自动布局和自动布线。很大程度上,布线是否成功和布线的质量的高低取决于设计规则的合理性,也依赖于用户的设计经验。 对于具体 ..

[查看全文]

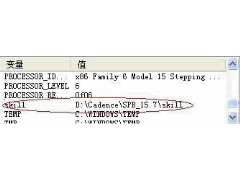

allegro加载skill函数到菜单

2013-01-12

Sutong

17

学习了一段时间allegro,你是不是也对SKILL函数有了一定的认识,也收集了不少skill函数吧,但是不是又对函数的应用感到麻烦和被动。现在就说一下怎样把函数加载到应用菜单,利用鼠标点击轻松执行。因为好多人不知道怎么使用,我也是摸索出来的,供大家参考,独乐乐,与人乐乐,孰乐?! 1、 设定环境变量 : 首先建立SKILL和SU ..

[查看全文]

Cadence 高速PCB的时序分析(1)

2013-01-09

宋宝华

21

1.引言 时序分析,也许是SI 分析中难度最大的一部分。我怀着满腔的期许给Cadence 的资深工程师发了一封e-mail,希望能够得到一份时序分析的案例,但是希望化作了泡影。资深工程师告诉我,他们还没有能够编写一个具体的案例。于是,我不得不将我的期许转化为自己研究并编写一个具体的案例,与广大PCB 工程师共享,令大彼天下P ..

[查看全文]

Protel DXP中元件库的使用

2013-01-08

18

目前在Protel DXP的试用版中只提供了两个集成元件库(integrated library)供使用,而要用到更多的Protel提供的元件库就必须从Protel网站下载,但许多朋友说从Protel网站下载的元件库在 Protel DXP不能使用或无法使用,又或者说使用中有错误提示。其实,这主要是我们对Protel DXP还不是非常了解。根据本人对Protel DXP的试 ..

[查看全文]

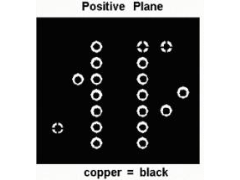

高速PCB设计指南(七)

2013-01-07

24

第一篇PCB基本概念1、“层(Layer) ”的概念与字处理或其它许多软件中为实现图、文、色彩等的嵌套与合成而引入的“层”的概念有所同,Protel的“层”不是虚拟的,而是印刷板材料本身实实在在的各铜箔层。现今,由于电子线路的元件密集安装。防干扰和布线等特殊要求,一些较新的电子产品中所用的印刷板不仅有上下两面供走线, ..

[查看全文]

Allegro约束管理器(Back-End)

2013-01-07

18

一、 约束管理器(BACK-END) 在HDL的相应课程中约束是表格代替PCB中的Constraints设置让人容易理解,这里用SigXplorer图形化可以更深刻的理解约束的定义和为什么。 (一)、规划网络(根据Cadence教程) 1、简单规划: 选取要操作的网络显示:Display/Blank Rats/All隐藏所有的网络,打开约束管理器,Display/Show Rats/Net切 ..

[查看全文]

PCB抗静电放电的措施

2013-01-06

12

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(ESD)对电子设备的干扰和破坏,需要采取多种技术手段进行 ..

[查看全文]

Protel如何打开Orcad格式的原理图

2013-01-05

DoDoPCB设计室:Tae

35

找到ORCAD的DSN文件...点右键,打开方式用PROTEL 99SE 打开的时候要求新建立一个工程...点OK. 点击YES,导入等待中…完成后就可以打开Orcad原理图了

[查看全文]

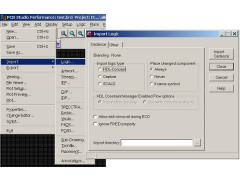

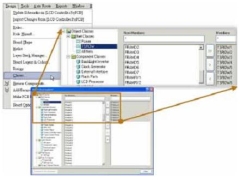

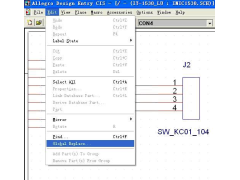

在Allegro 中如何输入原理图的网表(Netlist)文件?

2013-01-05

17

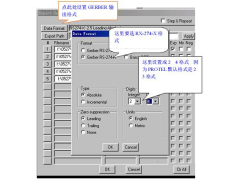

在Allegro 中执行File→Import→Logic…命令,得到输入逻辑(Import Logic)对话框。 在输入逻辑(Import Logic)对话框的Cadence 表格中选择相应的原理图输入类型(Import logic type)。例如,HDL-Concept、Capture (包括Capture CIS)或SCALD。 当你选择输入逻辑类型(Import logic type)为HDL-Concept 时, ..

[查看全文]

orcad中快速將所有零件的Footprint加上

2013-01-03

23

方法一 : 一页一页修改,打开某页,按CTRL+F->part->*,选中当前页所有器件,再点右键,选属性,在弹出对话框中按要修改REF 排序,用左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填入封装就成批修改了 方法二 : 先进入Project Manager,选择顶层原理图,选Edit-Browse Parts,用点击和Shift+点击选择所有元 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 60

-

高速PCB设计指南(三)2013年03月27日 155

-

PCB布线设计(二)2013年03月23日 45

-

混合信号PCB的分区设计2013年03月04日 31

-

高速PCB设计指南(六)2012年12月29日 32

-

PCB布线设计(一)2012年10月22日 13

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 51

-

常用电阻,电容,电感标称值2024年11月22日 94

-

PSPICE 的应用2013年04月06日 38

-

Protel DXP的电路仿真设计2013年04月04日 22

-

Gerber转protel的方法2013年04月04日 32

-

在PADS中添加表面型测试点2013年04月03日 57

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 385

-

Protel dxp等长走线2013年01月02日 333

-

Cadence 中添加工艺库文件步骤2013年01月16日 292

-

电气安全距离要求及分类2012年09月06日 276

-

Allegro铺铜的学习2012年12月05日 186

-

在ORCAD中整体修改网络名称2012年07月26日 177