高速PCB设计中的一些问题

2012-12-21

21

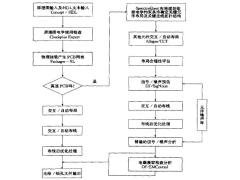

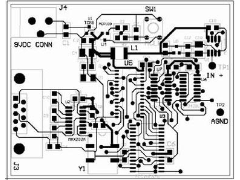

随着器件工作频率越来越高,高速PCB设计所面临的信号完整性等问题成为传统设计的一个瓶颈,工程师在设计出完整的解决方案上面临越来越大的挑战。尽管有关的高速仿真工具和互连工具可以帮助设计师解决部分难题,但高速PCB设计也更需要经验的不断积累及业界间的深入交流。布线拓扑对信号完整性的影响当信号在高速PCB板上沿传 ..

[查看全文]

高速PCB设计的叠层问题

2012-12-20

Ming

9

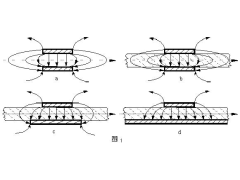

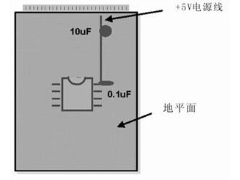

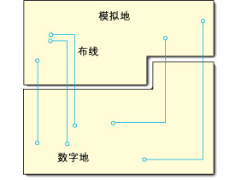

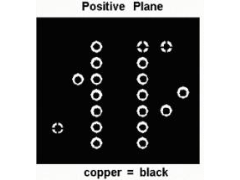

随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。在多层板的设计中,对于叠层的安排显得尤为重要。一个好的叠层设计方案将会大大减小EMI及串扰的影响,在下面的讨论中,我们将具体分析叠层设计如何影响高速电路的电气性能。 一.多层板和铺 ..

[查看全文]

ALLEGRO 约束规则设置步骤

2012-12-19

tzyhust@163.com

44

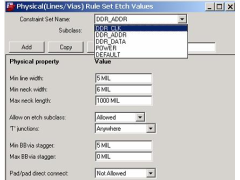

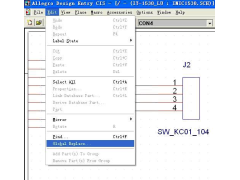

本文是我对约束规则设置方面的一些理解,希望对新手能有所帮助。由于本人水平有限,错误之处难免,希望大家不吝赐教! 在进行高速布线时,一般都需要进行线长匹配,这时我们就需要设置好 constraint 规则,并将这些规则分配到各类 net group 上。下面以 ddr为例,具体说明这些约束设置的具体步骤。 1. 布线要求 DDR 时钟:线宽 ..

[查看全文]

ORCAD传递分立器件Value值到PowerPCB的方法

2012-12-19

38

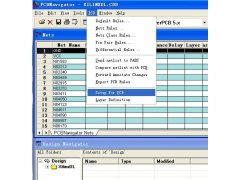

借助PCBNavigator,ORCAD与PowerPCB实现了很好的同步操作,但遗憾的是器件的Value值不能传递到PowerPCB,给人的感觉是ORCAD不如Powerlogic。经本人的摸索,找到了一种非常简单的办法,可以实现此功能。 1. 填写ORCAD的封装,即Footprint,此处必须填PowerPCB库中的Decal,而不是Part。 2. 在Orcad的Project M ..

[查看全文]

cadence 如何出具有盲埋孔的drill

2012-12-18

15

旧板适用 1 首先在MANUFACTURING Class 增加需要的钻孔图层(subclass);例如1-4-1的基板叠构需要(L1-L2),(L2-L5),(L5-L6)等三张钻孔图. 1.1 选择Setup>Subclass 指令. 1.2 在出现的Define Subclass 对话框内,选择MANUFACTURING 左边的按钮. 1.3 接著出现Define Non-conductor Subclass 对话框.在New Subclass 右边 ..

[查看全文]

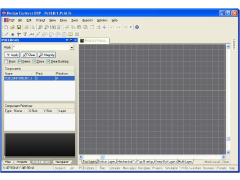

PowerPCB走线规则设置

2012-12-18

17

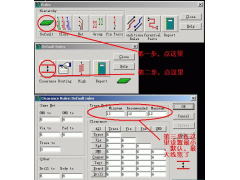

有朋友说POWERPCB布好局不会设置走线规则,比如默认线宽、安全线距等等,哪么我就截几个图片给大家看看吧! 下图设置走线默认线宽! 设置线与线及过孔、铺铜等相关规则参照下图设置就行了! 下面是如何设置等长线及相关网络的走线规则 首先按上图点NET 进入设置介面 然后选中其中要走等长的网络点HISPEED 进入设置介面,如 ..

[查看全文]

PCB Layout and SI 问答

2012-12-18

32

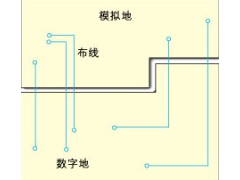

1.如何实现高速时钟信号的差分布线? 在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线? 专家解答: 信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴( ..

[查看全文]

Cadence EDA中PCB分析工具Specctraquest的使用

2012-12-18

李玉蓉

17

电子设计自动化(EDA)技术是目前进行电子产品设计中所采用的主要技术.设计者利用它可以设计出更完美的产品,并且极大地缩短了设计周期。但是随着电子技术的不断发展,在设计中,特别是在高速PCB的设计中出现了一些新的问题。例如:延时、串扰、电磁干扰等物理设计问题,迫切需要提供一些仿真分析工具来解决这些问题。本文 ..

[查看全文]

PCI总线布线的特殊要求

2012-12-17

15

PCI总线的布线有什么特殊要求 我们可以从下面的几点来分析一下PCI: 1 、首先,PCI系统是一个同步时序的体统,而且是Common clock方式进行的。 2、 PCI的电平特点是依靠发射信号叠加达到预期的电平设计。 3 、PCI系统一般是多负载的情况,一个PCI的桥片最多按照PCI的规范可以带6个负载(好像一般系统也不会操作5个)。 4、 PC ..

[查看全文]

PROTEL DXP创建元件封装

2012-12-17

54

指南的这一部分讲述以下主题: PROTEL DXP创建新的PCB 库 用元件向导为一个原理图元件创建封装 你可以在PCB 库里手工创建不常见的封装 using routing primitives within a footprint 建立一个封装,可以在PCB 编辑器中建立封装然后拷贝到一个PCB 库中,也可以在PCB 库中相互拷贝,或者用PCB 库编辑器的PCB 元件向导或画图工具 ..

[查看全文]

微波电路及其PCB设计

2012-12-16

30

一.关于CAD辅助设计软件与网络分析仪 对于高频电路设计,当前已经有了很好的CAD类软件,其强大的功能足以克服人们在设计经验方面的不足及繁琐的参数检索与计算,再配合功能强大的网络分析仪,按理应该是稍具经验者便能完成质量较好的射频部件。但是,实际中却不是这回事。 CAD设计软件依靠的是强大的库函数,包含了世界上绝 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 60

-

高速PCB设计指南(三)2013年03月27日 155

-

PCB布线设计(二)2013年03月23日 45

-

混合信号PCB的分区设计2013年03月04日 31

-

高速PCB设计指南(六)2012年12月29日 32

-

PCB布线设计(一)2012年10月22日 13

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 51

-

常用电阻,电容,电感标称值2024年11月22日 94

-

PSPICE 的应用2013年04月06日 38

-

Protel DXP的电路仿真设计2013年04月04日 22

-

Gerber转protel的方法2013年04月04日 32

-

在PADS中添加表面型测试点2013年04月03日 57

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 385

-

Protel dxp等长走线2013年01月02日 333

-

Cadence 中添加工艺库文件步骤2013年01月16日 292

-

电气安全距离要求及分类2012年09月06日 276

-

Allegro铺铜的学习2012年12月05日 186

-

在ORCAD中整体修改网络名称2012年07月26日 177