Ground via的位置对高频特性的影响

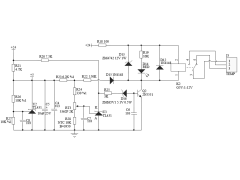

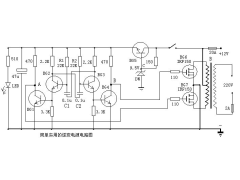

图6是为了量测870~890MHz高频增幅电路的特性,特别设计的仿真分析用电路,具体而言它在诱电体厚度为1.0mm, εr=4.3的CEM-3印刷电路板上进行封装,测试如何才能获得10dB以上的等化,以及1.1以下的VSWR(Voltage standing Wave Ratio)特性。

图6 870~890MHz高频增幅器的电路(仿真分析用电路)

ground via尽可能靠近pad

如图6的电路可知Transistor的emitter端子与ground之间插入micro strip line model,当作emitter的pad至ground via之间印刷pattern,藉此测试印刷pattern的长度,亦即emitter的pad至ground via之间的距离对高频特性的影响。等化特性、输出入阻抗特性(impedance)的测试结果分别如下所述:

等化特性

图7是emitter直接与ground连接,以及emitter的pad至ground via之间相隔2.0mm时,两者的通过特性模拟分析结果。图7(a)是配合模拟分析将LX 设定为1μm的结果;表4是上述两者等化的差异结果。由图可知即使是800MHz领域由于插入2.0mm的pad,等化大约会降低3.4~4.4dB。

图7 Emitter的pad至ground via的距离造成通过特性的差异

|

频率 |

等化(dB) |

等化差异 |

|

|

(MHz) |

Emitter直接与ground连接 |

LX = 2.0mm 时 |

(dB) |

|

800 |

14.5816 |

10.1609 |

-4.4207 |

|

880 |

16.1218 |

12.1539 |

-3.9679 |

|

900 |

15.5556 |

12.1961 |

-3.3595 |

输出入阻抗特性

图8的Smith chart是emitter直接与ground连接,以及emitter的pad至ground via之间相隔2.0mm时,Transistor (Tr1)的输出入阻抗(S11,S22) 频率特性仿真分析结果。由Smith chart可知图中有S11 与S22 两条特性曲线,它的中心是50Ω阻抗(imped ance),VSWR是图中1.0的点。从Smith chart的中心(50Ω)描绘的两个同心圆表示 VSWR,内侧圆的VSWR为1.5,外侧圆的VSWR为2.0。由图8(a)可知emitter直接与ground连接的场合,880MHz的输入阻抗 S11与输出阻抗S22 几乎都是50Ω,由此可知两者接近一致(matching)。ground pad在2.0 (LX = 2.0 mm)的位置时,880MHz的输出入阻抗是在VSWR=2.0圆的外侧上,大幅偏离50Ω的整合条件。

(a)emitter直接与ground连接时的阻抗特性

(b) 距离emitter pad2mm设有ground via时的阻抗特性

图8 Emitter的pad至ground via的距离造成阻抗特性的差异

根据以上模拟分析结果可知为了获得良好的高频电路特性,因此高频电子组件的ground via必需设在pad的近傍。

大直径via较有利

图6的Transistor emitter pad分别设有直径0.4mm与0.2mm的via,如果与图9的电路作增幅特性差异比较,此处假设via直径以外的条件,例如模拟分析手法与图6设有v ia完全相同,且 为0.001mm。根据以上测试条件获得如图10所示的通过特性,需注意的是图10的via直径分别是0.4mm与0.2mm;表5是两者的等化差异,由表5可知不同的via直径会造成-0.5~-0.6dB的等化差异,如果与表5的「emitter直接与ground连接时的通过特性」比较时,via直径0.4mm的等化值为-1.3~-1.9dB;via直径0.2m m的等化值为-1.8~-2.5dB。图11是via直径为0.4mm与0.2mm时的输出入阻抗特性,由图11可知via直径为0.4mm的VSWR为1.4;via直径为0.2mm的VSWR为1.6,也就是说直径为0.4mm的via对整合状态的影响比较小。

图9 870~890MHz高频增幅器的电路(仿真分析用电路)

图10 不同的ground via直径离造成通过特性的差异

|

频率 |

等化(dB) |

等化差异 |

|

|

(MHz) |

ground via直径0.4mm |

ground via直径0.2mm |

(dB) |

|

800 |

12.715 |

12.0742 |

-0.6408 |

|

880 |

14.5017 |

13.9251 |

-0.5766 |

|

900 |

14.2372 |

13.7487 |

-0.4885 |

图11 不同的ground via直径造成等化的差异(Smith chart)

-

一款高温报警电路2024年11月13日 81

-

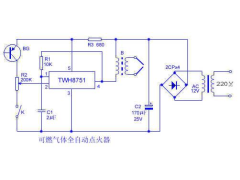

可燃气体全自动点火器2012年09月22日 76

-

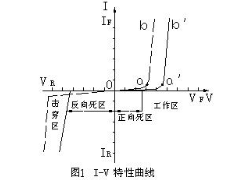

LED参数与特性2012年09月18日 118

-

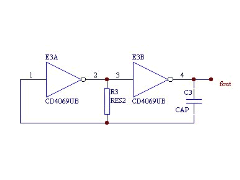

RC振荡电路的几种接法2012年09月10日 221

-

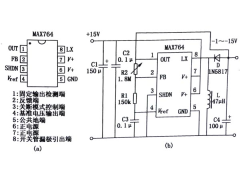

MAX764极性反转电路2012年08月24日 47

-

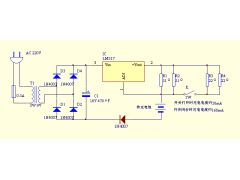

实用恒流充电器2012年08月18日 175

-

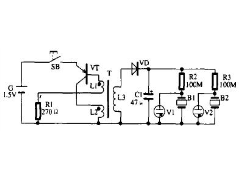

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4874

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

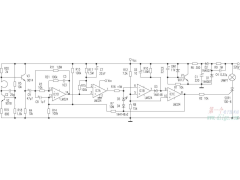

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499