PROTEL DXP2004 DRC规则英文对照

2013-03-14

20

在PROTEL DXP2004中的DRC规则检查项目,对于一些英文水平较薄弱的朋友是一个大难题,特和同事对其进行整理一下,英文水平有限,仅供参考: PROTEL DXP2004 DRC 规则英文对照 一、Error Reporting 错误报告 A:Violations Associated with Buses 有关总线电气错误的各类型(共12项) bus indices out of range 总线分支索引超出 ..

[查看全文]

Protel PCB导出元件清单方法

2013-03-14

22

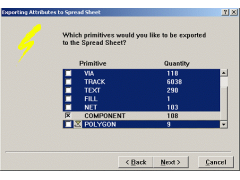

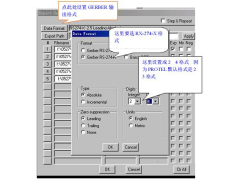

打开PCB文件,选择 Edit-----Export to spread。在弹出图中选择如下内容: 之后导出清单。用Excel 2003打开。新建 “空白工作簿”把清单内容复制到新工作簿中再进行编辑。

[查看全文]

关于protel内电层分割

2013-03-13

大炮

16

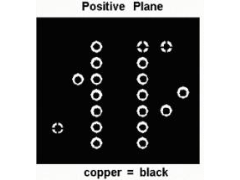

PROTEL99的电性图层分为两种,打开一个PCB设计文档按,快捷键L,出现图层设置窗口。左边的一种(SIGNAL LAYER)为正片层,包括TOP LAYER、BOTTOM LAYER和MIDLAYER,中间的一种(INTERNAL PLANES)为负片层,即INTERNAL LAYER。这两种图层有着完全不同的性质和使用方法。 正片层一般用于走纯线路,包括外层和 ..

[查看全文]

Allegro使用问题解答

2013-03-09

19

1、问:我在产生NC TAPE 文件时提示error,但并没有生成NCTAPE.LOG 可供查找错误原因,望高手帮助! 答:NCTAPE.LOG 的内容其实也就是执行File/Viewlog 命令弹出的文本中的内容。您可以通过这个来查看,您不能产生log 文件的原因可能是软件的关于TEXT 的路径设置有问题。您可以去SETUP/USER PERFERENCE 中的CONF ..

[查看全文]

protel四层板及内电层分割入门

2013-03-08

古风

34

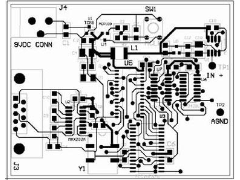

本教程将详细的讲解Protel 99SE的四层板的设计过程,以及在其中的内电层分割的用法。 事先声明:本教程用于初学者的入门与提高;对于高手们,也欢迎看看,帮小弟指出其中不当的做法! 下面,就打开你的电脑及软件开始了。(- - - - - -好像是废话, 嘿嘿..... ) 一、准备工作 新建一个DDB文件,再新建相关的原理图文件, 并做好相关 ..

[查看全文]

Allegro元件封装(焊盘)制作方法总结

2013-03-08

BabyKing

16

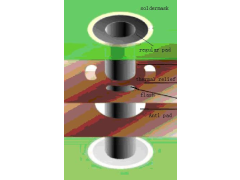

在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。元件封装大体上分两种,表贴和直插。针对不同的封装,需要制作不同的Padstack。 Allegro中Padstack主要包括以下部分 。 1、PAD即元件的物理焊盘 pad有三种: Regular Pad,规则焊盘(正片中)。可以是:Circle 圆型、Square 方型、Oblong 拉长圆型 ..

[查看全文]

PCB分层堆叠在控制EMI辐射中的作用和设计技巧

2013-03-07

Rick Hartley

12

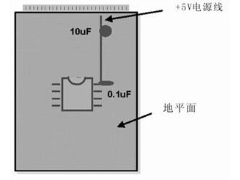

解决EMI问题的办法很多,现代的EMI抑制方法包括:利用EMI抑制涂层、选用合适的EMI抑制零配件和EMI仿真设计等。本文从最基本的PCB布板出发,讨论PCB分层堆叠在控制EMI辐射中的作用和设计技巧。 电源汇流排在IC的电源引脚附近合理地安置适当容量的电容,可使IC输出电压的跳变来得更快。然而,问题并非到此为止。由於电容 ..

[查看全文]

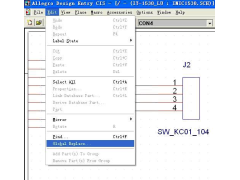

如何在Capture中定义Swap功能在Allegro中实现Swap?

2013-03-06

33

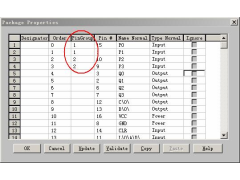

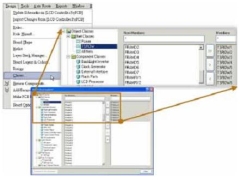

一、Pin Swap1.当线路图设定完成后,点选所要进行Swap Pin的元器件,点击右键,在下拉菜单中选择Edit Part,进入零件的编辑视窗。或者直接在编辑Part界面下做以下动作。2.点选菜单View >Package3.点选菜单Edit>Properties,弹出下面的对话框: 4.在对话框中有一栏PinGroup,即用于设定零件Pin脚是否可以进行 ..

[查看全文]

orcad 的元件库列表

2013-03-06

19

1、AMPLIFIER.OLB 共182 个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093 等。 2、ARITHMETIC.OLB 共182 个零件,存放逻辑运算IC,如TC4032B,74LS85 等。 3、ATOD.OLB 共618 个零件,存放A/D 转换IC,如ADC0804,TC7109 等。 4、BUS DRIVERTRANSCEIVER.OLB 共632 个零件,存放汇流排驱动IC,如74 ..

[查看全文]

orcad转mentor_expedition

2013-03-05

swordfish

13

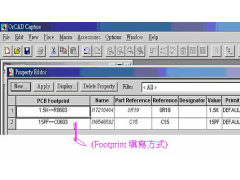

使用Orcad画电路图后,将每一个零件的PCB Footprint填入,格式如下图所示 电路完成后,确认DRC没有问题,即可生成网络表,选取DSN后,选择Tools→Create Netlist→点选Other→选择intergra.dll格式 生成网络表的档名为:netlist.kyn 接著将netlis.kyn档案COPY到Expedition专案目录下的logic目录。 假设你目前 ..

[查看全文]

混合信号PCB的分区设计

2013-03-04

31

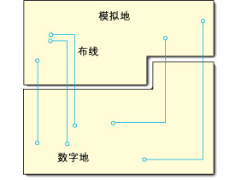

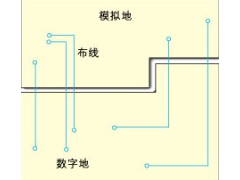

摘要:混合信号电路PCB的设计很复杂,元器件的布局、布线以及电源和地线的处理将直接影响到电路性能和电磁兼容性能。本文介绍的地和电源的分区设计能优化混合信号电路的性能。 如何降低数字信号和模拟信号间的相互干扰呢?在设计之前必须了解电磁兼容(EMC)的两个基本原则:第一个原则是尽可能减小电流环路的面积;第二个原 ..

[查看全文]

基于Cadence的高速PCB设计

2013-03-04

张汝金 刘琨

17

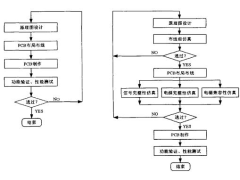

1 引言随着人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快.相应的高速PCB的应用也越来越广,设计也越来越复杂.高速电路有两个方面的含义:一是频率高,通常认为数字电路的频率达到或是超过45MHz至50MHz,而且工作在这个频率之上的电路已经占到了整个系统的三分之一,就称为高速电路.另外从信号的上升与 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 60

-

高速PCB设计指南(三)2013年03月27日 155

-

PCB布线设计(二)2013年03月23日 45

-

混合信号PCB的分区设计2013年03月04日 31

-

高速PCB设计指南(六)2012年12月29日 32

-

PCB布线设计(一)2012年10月22日 13

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 51

-

常用电阻,电容,电感标称值2024年11月22日 94

-

PSPICE 的应用2013年04月06日 38

-

Protel DXP的电路仿真设计2013年04月04日 22

-

Gerber转protel的方法2013年04月04日 32

-

在PADS中添加表面型测试点2013年04月03日 57

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 385

-

Protel dxp等长走线2013年01月02日 333

-

Cadence 中添加工艺库文件步骤2013年01月16日 292

-

电气安全距离要求及分类2012年09月06日 276

-

Allegro铺铜的学习2012年12月05日 186

-

在ORCAD中整体修改网络名称2012年07月26日 177