SVPWM信号发生器的VHDL实现

2012-06-02

吴晨光

11

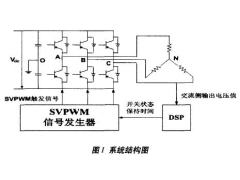

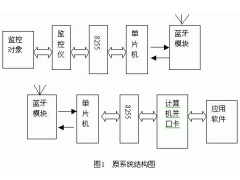

近年来,DSP在SVPWM(空间矢量脉宽调制)控制领域得到了广泛应用。但是使用DSP单核心的控制方法仍然存在一些缺陷:基于软件的:DSP在实现SVPWM触发信号时需要较长的时钟周期;微处理器中不确定的中断响应会导致PWM脉冲的相位抖动。针对以上问题,本文提出了一种利用FPGA实现的SVPWM信号发生器,系统结构如图1所示 ..

[查看全文]

verilog设计经验

2012-06-02

10

一、组合逻辑 1、敏感变量的描述完备性 Verilog中,用always块设计组合逻辑电路时,在赋值表达式右端参与赋值的所有信号都必须在 always @(敏感电平列表)中列出,always中if语句的判断表达式必须在敏感电平列表中列出。如果在赋值表达式右端引用了敏感电平列表中没有列出的信号,在综合时将会为没有列出的信号隐含地产生一个透 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第一章 安装)

2012-06-02

44

第1章 安装 OrCAD 10.3 Release1.1 OrCAD 10.3 Release安装建议的计算机配置1.1.1 OrCAD 10.3 Release 窗口操作系统OrCAD 10.3 Release可以执行在下列2 种Microsoft 窗口操作系统:(1)Windows 2000(SP4)(2)Windows XP Professional, or Windows XP Home Edition注:OrCAD10.3 Release已不再支持Windows NT 窗 ..

[查看全文]

ModelSim下用SystemC做设计验证方法与示例

2012-06-02

13

最近用SystemC做验证做上瘾了,写一个小文吧。 如何在ModelSim下编译和仿真SystemC的设计? 如何在ModelSim下用SystemC的做验证? SystemC作为一种系统级设计与验证语言,非常适合做复杂IC的验证,而不是用于RTL描述。很多人问我如何将SystemC综合和编译为可以下载的CPLD/FPGA的比特文件或者综合为ASIC网表,我的 ..

[查看全文]

Nios II程序下载到Flash的方法

2012-06-02

lotol

9

我们在调试完Nios II系统后,接下来的工作就是要把程序固化到NOR Flash(以下简称Flash)中,让其上电后自动运行。但是这又该如何做呢?我想大家一定会想到使用Nios的Flash Programmer。没错,就是用它。不过,Flash Programmer也不是随便拿来就能用的,如果设置不正确,照样无法使用。闲话少说,follow me。 说明:设置 ..

[查看全文]

modelsim仿真ROM

2012-06-02

8

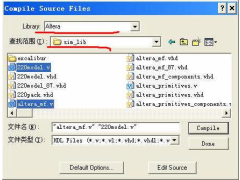

一、主要环境参数是 : modelsim SE 6.1b+Quartus II 5.1 SP2 HDL 是verilog。 器件是Stratix II EP2S90F1020 采用两种方法设计ROM,ROM的容量是1000×2×16bit。因为需要COS 和SIN 两种数据。 第一种采用Altera 的LPM 生成ROM,ROM 的内容也是利用Quartus 生成hex 文件,之所以不采用mif 文件的原因是因为在modelsim不 ..

[查看全文]

Verilog Pli的基本使用方法(modelsim)

2012-06-02

17

内容未做证实,仅供参考。 1.hello.c文件内容 #include #include "veriuser.h" static PLI_INT32 hello() { printf("Hi there\n"); return 0; } s_tfcell veriusertfs[] = { {usertask, 0, 0, 0, hello, 0, "$hello"}, {0} /* last entry must be 0 */ }; 2.hello.v文件内容 module hello; initial begin $hello ..

[查看全文]

基于单片机P89C61X2的FPGA配置

2012-06-02

胡远望

8

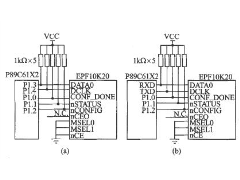

大部分FPGA采用基于SRAM(静态随机存储器)的查找表逻辑形成结构,就是用SRAM构成逻辑函数发生器。SRAM工艺的芯片在掉电后信息就会丢失,需要外加一片专用配置芯片。在上电时,由这个专用配置芯片把数据加载到FPGA中,然后FPGA就可以正常工作。这就是在线可重配置ICR(In-Circuit Reconfigurability)方式。 Altera公 司生 ..

[查看全文]

MultiSIM 电子仿真软件使用技巧

2012-06-02

朱秋龙

127

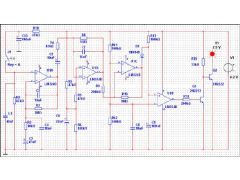

众所周知,电子仿真软件MultiSIM最初由加拿大的IIT 公司推出,从Multisim2001开始到后来的Multisim7和Multisim8止;Multisim9到目前的Multisim10版本,已改由美国国家仪器公司(NI公司)所推出。Multisim版本每次升级,软件功能都有相应的提高,但它们的操作方法和电子电路虚拟仿真这一块内容几乎没有太大的变化。也就是说 ..

[查看全文]

蓝牙HCI-UART与并口的FPGA控制接口设计

2012-06-02

12

摘要:某应用蓝牙技术的医疗监控系统中,单片机是其数据传输瓶颈。本设计采用FPGA取代了原系统的单片机和8255芯片,使数据传输速率提高了近10倍。文中讨论了设计的一些关键问题。 1 引言 在蓝牙体系的实现方案中, HCI意义重大,它以一个统一的接口实现主机设备与蓝牙模块之间的互操作。蓝牙HCI层定义了数据、命令、事件三类 ..

[查看全文]

FPGA的FIR抽取滤波器的设计

2012-06-02

佟力永

10

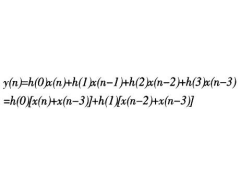

1、引言 抽取滤波器广泛应用在数字接收领域,是数字下变频器的核心部分。目前,抽取滤波器的实现方法有3种:单片通用数字滤波器集成电路、DSP和可编程逻辑器件。使用单片通用数字滤波器很方便,但字长和阶数的规格较少,不能完全满足实际需要。使用DSP虽然简单,但程序要顺序执行,执行速度必然慢。现场可编程门阵列(FPGA ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310