如何计算FPGA设计频率

2012-06-02

26

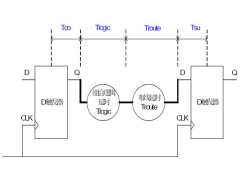

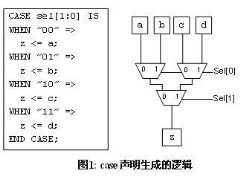

我们的设计需要多大容量的芯片?我们的设计能跑多快?这是经常困扰工程师的两个问题.对于前一个问题,我们可能还能先以一个比较大的芯片实现原型,待原型完成再选用大小合适的芯片实现.对于后者,我们需要一个比较精确的预估,我们的设计能跑50M,100M 还是133M? 首先让我们先来看看Fmax 是如何计算出来的.图(1)是一个通用的模 ..

[查看全文]

VHDL设计举例:步进电机控制器

2012-06-02

24

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.ALL; USE IEEE.std_logic_arith.ALL; ENTITY step_motor IS PORT( f, p, d: INSTD_LOGIC:='0'; speed : inSTD_LOGIC_VECTOR(1 downto 0); coil : OUTSTD_LOGIC_VECTOR(3 downto 0) ); END step_motor; ARCHITECTURE behavior OF s ..

[查看全文]

怎样写testbench

2012-06-02

11

本文的实际编程环境:ISE 6.2i.03 ModelSim 5.8 SE Synplify Pro 7.6 编程语言 VHDL 在ISE 中调用ModelSim 进行仿真 一、 基本概念和基础知识 Testbench 不仅要产生激励也就是输入,还要验证响应也就是输出。当然也可以只产生激励,然后通过波形窗口通过人工的方法去验证波形,这种方法只能适用于小规模的设计。 在ISE 环境中, ..

[查看全文]

常用的微波EDA仿真软件介绍

2012-06-02

19

1.引言 微波系统的设计越来越复杂,对电路的指标要求越来越高,电路的功能越来越多,电路的尺寸要求越做越小,而设计周期却越来越短。传统的设计方法已经不能满足系统设计的需要,使用微波EDA软件工具进行微波元器件与微波系统的设计已经成为微波电路设计的必然趋势。随着单片集成电路技术的不断发展,GaAs、硅为基础的微波 ..

[查看全文]

Altera FPGA、CPLD 学习笔记

2012-06-02

10

1.硬件设计基本原则 速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用 & ..

[查看全文]

fir滤波器的Verilog程序

2012-06-02

35

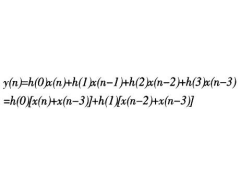

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date:17:01:38 10/09/06 // Design Name: // Module Name:ppeifir // Project Name: // Target Device: // Tool versions: // Description:用Verilog编写的fir滤波器程 ..

[查看全文]

FPGA的FIR抽取滤波器的设计

2012-06-02

佟力永

10

1、引言 抽取滤波器广泛应用在数字接收领域,是数字下变频器的核心部分。目前,抽取滤波器的实现方法有3种:单片通用数字滤波器集成电路、DSP和可编程逻辑器件。使用单片通用数字滤波器很方便,但字长和阶数的规格较少,不能完全满足实际需要。使用DSP虽然简单,但程序要顺序执行,执行速度必然慢。现场可编程门阵列(FPGA ..

[查看全文]

Multisim 10仿真实验

2012-06-02

12

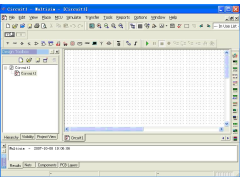

一、 实验目的 熟悉并掌握Multisim10对单片机的仿真过程。 加深对单片机硬件以及软件理论知识的理解。 二、 实验原理 1、Multisim10 美国国家仪器公司下属的ElectroNIcs Workbench Group在今年年初发布了Multisim 10。新版的Multisim10,加入了MCU模块功能,可以和8051等单片机进行编程联调,该软件元件丰富,界面直观,虚拟 ..

[查看全文]

复用器重构降低FPGA成本

2012-06-02

12

摘要 本文介绍了一种新的能够降低FPGA实际设计20%成本的综合算法。该算法通过减少复用器所需查找表(LUT)的数量来实现。算法以效率更高的4:1复用器替代2:1复用器树。算法性能关键在于寻找总线上出现的复用器数量。新的优化方法占用一定的逻辑,这些逻辑由总线进行分担,从而减少了总线上每个比特位所需的逻辑。 1.引言 复 ..

[查看全文]

Nios II开发常见问题

2012-06-02

9

许多朋友在进行Nios II系统的学习,开发中,常常会遇到许多问题;我也会经常接到许多E-Mail,以及电话,询问一些nios开发中的问题。我对这些问题进行了总结,写成了这篇文章。如果本文能对您有一点点帮助,我都会感到非常高兴。 对于许多问题,您仍然需要参考Altera提供的官方参考文档以及随机的help文档。 一。硬件相关: 1.EP ..

[查看全文]

IIR数字滤波器的FPGA实现

2012-06-02

魏国华

8

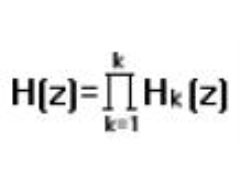

摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此设计扩展性好,便于调节滤波器的性能,可以根据不同的要求在不同规模的FPGA上加以实现。 IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同 ..

[查看全文]

基于CPLD的交通灯控制系统

2012-06-02

孙芹芝 张瑾 苏晓鹭

18

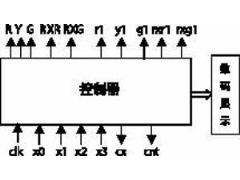

引言 EDA技术是用于电子产品设计中比较先进的技术,可以代替设计者完成电子系统设计中的大部分工作,而且可以直接从程序中修改错误及系统功能而不需要硬件电路的支持,既缩短了研发周期,又大大节约了成本,受到了电子工程师的青睐。 实现路口交通灯系统的控制方法很多,可以用标准逻辑器件、可编程序控制器PLC、单片机等方案 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310