Nios II在电机伺服控制中的应用

2012-06-02

8

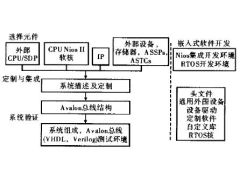

1 引言 Nios II系列32位RISC嵌入式处理器是Altera公司的第二代软核嵌入式处理器,性能超过200DMIPS Nios II处理器是软核,开发者能够从无限的系统配置组合中选择满足性能和成本目标的方案,而不必为系统级设计采用ASIC,这种开发方式非常适合设计针对网络、电信、数据通信、嵌入式和消费市场的各种嵌入式应用。本文采用Nios ..

[查看全文]

基于FPGA的多路脉冲重复频率跟踪器

2012-06-02

12

摘要:在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟踪器,它解决了在密集信号环境下信号跟踪的实时性问题,减小了系统体积。经过实验验证,其各项指标均达到了设计要求。 随着高科技的迅速发展,现代战争已经不仅是传统意义战场上 ..

[查看全文]

我的仿真工作流程(Verilog/Modelsim+Debussy)

2012-06-02

29

这是献给大家的第二篇,文章详细说明了本人近一年来,自己摸索出来的一套仿真工作流程。接触过Modelsim这类软件的朋友可能都会感觉上手比较困难,原因有二:一、对仿真机制不了解,对基于source+testbench的工作流程不熟悉(大多数朋友接触FPGA仿真可能以waveform的方式);二、对软件的安装和使用不熟悉,Modelsim软 ..

[查看全文]

ModelSim SE仿真Altera库的建立

2012-06-02

shemily

25

(注:最近自己准备做后仿真,到坛子里看看了,发现一开始建库就是一个很大的问题。为了便以自己学习也为了给大家省点事,我花了十来个小时整理了一些资料,全部资料来自edacn.net/bbs的ModelSim的〈库〉,在下面的资料中不能一一列出作者,请各位网友多多包涵。下面的资料是大家的成果。by CHY 07.04.05) 1. modelsim怎 ..

[查看全文]

静态时序分析在高速FPGA设计中的应用

2012-06-02

周海斌

28

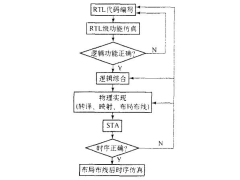

摘要:介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进时序收敛的方法。结合设计实例,阐明了STA在高速、大规模FPGA开发中的应用。实践表明,随着数字设计复杂度的增加,在后端的时序验证环节,与传统的动 ..

[查看全文]

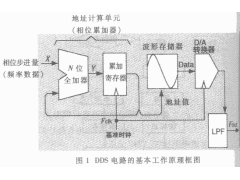

FPGA直接数字频率合成器的设计

2012-06-02

周俊峰 陈 涛

7

摘要:介绍了利用Altera的FPGA器件(ACEX EP1K50)实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。 关键词:直接数字频率合成(DDS) 现场可编程门阵列(FPGA) 直接数字频率合成(Direct Digital Fraquency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需要波形的一种新的频率 ..

[查看全文]

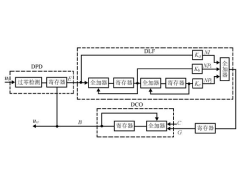

基于FPGA 的高阶全数字锁相环的设计与实现

2012-06-02

单长虹 王彦 陈文光 陈忠泽

6

摘要:提出了一种实现高阶全数字锁相环的新方法。该锁相环以数字比例积分控制取代了传统的一些数字环路滤波控制方法,具有电路结构简单、控制灵活、跟踪精度高、环路性能好和易于集成的特点。文中介绍了该高阶全数字锁相环的系统结构和工作原理,对其性能进行了理论分析和计算机仿真。应用EDA 技术设计了该系统,并用FPGA实 ..

[查看全文]

利用有限状态机控制A/D采样

2012-06-02

14

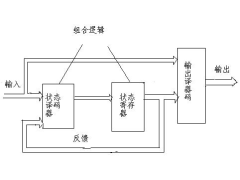

1 状态机的基本结构和功能 状态机是一类很重要的时序电路,是许多数字电路的核心部件。状态机的一般形式如图1所示。除了输入信号、输出信号外,状态机还包括一组寄存器,它用于记忆状态机的内部状态。状态机寄存器的下一个状态及输出,不仅同输入信号有关,而且还于寄存器当前状态有关。寄存器可以认为是组合逻辑和寄存器逻辑 ..

[查看全文]

基于NIOS II嵌入式处理器实现LCD的控制

2012-06-02

廖红华 程涛

12

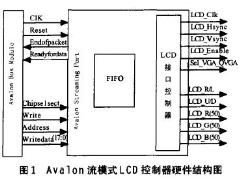

随着半导体技术以及计算机软硬件技术的飞速发展,对于图像的显示的控制技术也呈现出越来越多的方式。本文介绍了一种基于NIOS II软核处理器实现对LCD-LQ057Q3DC02控制的新方法。在设计中利用FPGA的Altera的SOPC Builder定制NIOS II软核处理器及其与显示功能相关的“软” 硬件模块来协同实现显示控制的软硬件设 ..

[查看全文]

FPGA有限状态机模拟I2C总线设计

2012-06-02

潘小冬

18

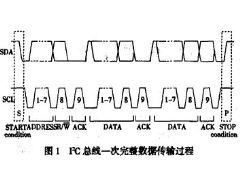

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模 ..

[查看全文]

ModelSim se完全编译Xilinx库文件

2012-06-02

16

什么是之前的老办法呢? Modlesim 仿真库的建立: 将Modelsim根目录下的modelsim.ini的属性由只读改为可写。 新建一个文件夹,比如library(为叙述方便,把它放在modelsim的根目录下)。D:/modelsim/library. 启动Modelsim,选择[File]/[chang Directory],选择D:/modelsim/library. 选择[File]/[New]/[library]命令,弹出[C ..

[查看全文]

利用ModelSim SE6.0C实现时序仿真

2012-06-02

16

1) 打开一个工程文件。 2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。在右边出现的设置栏中将“Tool name”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310