16*16bit并行乘法器设计

2012-06-02

7

构成并行乘法器的三个部分:部分积,华莱氏树,加法器。源程序也比较大,我也就挑这三个部分中的一些贴出来,我想这样也就足够了。如果各位网友,也想写的话,并且有困难的话,我将在能力范围之内提供帮助。这个乘法器我采用了5级流水线,10k20lab占用70%(其实还可以更少),速度46M(EP1C3可以跑到150M)。部分积:a ..

[查看全文]

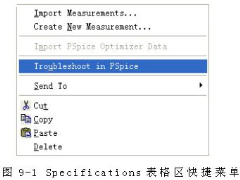

从实例中学习OrCAD-PSpice 10.3-AA(第9章 仿真的故障排除)

2012-06-02

48

第9章 仿真的故障排除 在运行高级分析工具的过程中,由于操作失误、参数设置不合理等方面的原因,常常出现错误信息或者系统仿真不能运行等情况,用户往往得不到理想的分析结果,面对这些存在的难题,不能坐着发闷,要积极的解决问题。本章主要介绍运用故障排除分析工具解决存在问题的使用方法及高级分析中一般性故障的解决方 ..

[查看全文]

FPGA实现信号延时的方法

2012-06-02

19

FPGA实现信号延时的方法汇总: 1、门延时数量级的延时(几个ns),可用逻辑门来完成,但告诉综合器不要将其优化掉(不精确,误差大,常常不被推荐)。比如用两个非门(用constraint 来告诉synthesizer 不要综合掉这些逻辑)。 2、使用delay cell,lcell。 3、采用更快的时钟,通过计数器来实现,对于比较小的延时,用两个DFF 级联就 ..

[查看全文]

ISE仿真中需要注意的问题

2012-06-02

iamfrankie

14

在我们团队负责的项目光栅传感器系统高频并行解调算法的FPGA实现中,需要直接频率合成模块,因此我们想在FPGA上实现一个DDS芯片的功能,最近在BASYS板上调通了DDS模块,在功能仿真过程中我们发现在ISE环境下编写VHDL时对信号赋初值对仿真是十分必要的。 由于参数的要求模块中用到了一个三分频电路。程序如下: library ..

[查看全文]

嵌入式处理器Nios II与液晶显示模块的接口及应用

2012-06-02

包明 余成波

10

液晶显示器(LCD)由于具有工作电压低、功耗低、体积小、显示信息量大、寿命长、不产生电磁辐射污染、可以显示复杂的文字及图形等优点,液晶显示器已被广泛应用于各种仪器仪表、电子设备及控制领域中,成为测量结果显示和人机对话的重要工具。液晶显示器按其功能可分为笔段式和点矩阵式液晶显示器,后者又可以分为字符点阵式 ..

[查看全文]

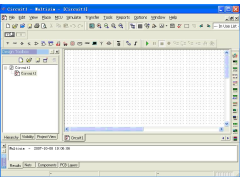

Multisim 10仿真实验

2012-06-02

12

一、 实验目的 熟悉并掌握Multisim10对单片机的仿真过程。 加深对单片机硬件以及软件理论知识的理解。 二、 实验原理 1、Multisim10 美国国家仪器公司下属的ElectroNIcs Workbench Group在今年年初发布了Multisim 10。新版的Multisim10,加入了MCU模块功能,可以和8051等单片机进行编程联调,该软件元件丰富,界面直观,虚拟 ..

[查看全文]

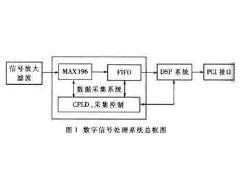

用Verilog HDL设计自动数据采集系统

2012-06-02

11

随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。从电子CAD、电子CAE到电子设计自动化(EDA ..

[查看全文]

奇数次分频器

2012-06-02

9

奇数次分频器 module count(out,clk,clr); parameter N=5; output out; input clk,clr; reg out1,out2; reg [N/2:0] count1,count2; always @(posedge clk or posedge clr ) if(clr) begin count1=0; out1=0; end elsebegin count1 = count1 + 1; if( count1 == ((N+1)/2)) out1 =!out1; else if (count1==N) begin out1=~out1; coun ..

[查看全文]

ADC0809 VHDL控制程序

2012-06-02

50

--文件名:ADC0809.vhd --功能:基于VHDL语言,实现对ADC0809简单控制 --说明:ADC0809没有内部时钟,需外接10KHz~1290Hz的时钟信号,这里由FPGA的系 --统时钟(50MHz)经256分频得到clk1(195KHz)作为ADC0809转换工作时钟。 --最后修改日期:2004.3.20 library ieee; use ieee.std_logic_1164.all; use ieee.std ..

[查看全文]

在Nexar上实现一个完整的嵌入式系统

2012-06-02

7

以下我们将结合一个实例来简要介绍一下如何在Nexar上实现一个完整的嵌入式系统设计过程。 首先:创建一个新的FPGA工程 1、选择菜单[menus]File>>New>>FPGA Project,在工程栏中将会显示新建的FPGA工程名,选择菜单[menus]File>>Save Project,在对话框中修改工程名称,然后Save。在工程栏中选择File View选项,在工程 ..

[查看全文]

FPGA四阶IIR数字滤波器实现

2012-06-02

10

常用的数字滤波器有FIR数字滤波器和IIR数字滤波器。FIR数字滤波器具有精确的线性相位特性,在信号处理方面应用极为广泛,而且可以采用事先设计调试好的FIR数字滤波器IPCore来完成设计,例如Altera公司提供的针对Altera系列可编程器件的MegaCore,但是需要向Altera公司购买或申请试用版。另外,对于相同的设计指 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第6章 蒙特卡洛工具)

2012-06-02

35

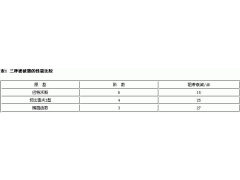

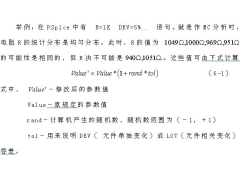

第6章 蒙特卡洛(Monte Carlo)工具的使用 PSpice一直重视所设计的电路,要能适合于批量生产的需要。现在PSpice10.3单独设立Monte Carlo工具,使这一项工作得到加强。本章先简介容差分析的基本概念,其后重点介绍Monte Carlo工具的使用方法。 6.1容差分析 前几章所述电路分析法时,已经提过只将元件视作理想元件按标称值进 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310