Verilog阻塞式赋值与非阻塞式赋值的分析

2012-06-02

nsun

19

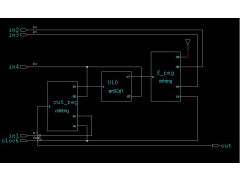

在Verilog HDL中,有两种过程性赋值方式,即阻塞式(blocking)和非阻塞式(non-blocking)。这两种赋值方式看似差不多,其实在某些情况下却有着根本的区别,如果使用不当,综合出来的结果和你所想得到的结果会相去甚远。 Tip:所谓过程性赋值就是指在initial或always语句内的赋值,它只能对寄存器数 据类型的变量赋值。 阻塞式 ..

[查看全文]

TEXTIO及其在VHDL仿真中的应用

2012-06-02

于红旗

16

TEXTIO 在VHDL 仿真与磁盘文件之间架起了桥梁,使用文本文件扩展VHDL 的仿真功能。本文介绍TEXTIO 程序包,以一个加法器实例说明TEXTIO 的使用方法,最后使用ModelSim 对设计进行仿真,并分析仿真结果。 在对VHDL 源程序进行仿真时, 由于有的输入输出关系仅仅靠输入波形或编写testbench 中的信号输入是难以验证结果正确 ..

[查看全文]

VHDL语言程序配置EAB的研究

2012-06-02

何永泰

60

摘要: 在FPGA(现场可编程门阵列)的使用中,要将VHDL(甚高速集成电路硬件描述语言)编写的程序配置到EAB(嵌入式阵列块)单元中,会遇到许多问题,配置很难成功。根据配置EAB的经验,详细介绍了正确配置EAB的方法。 1、引言 FLEX10K器件是工业界第一个嵌入式的PLD(可编程逻辑器件),由于其具有高密度、低成本、低功率等特点,成 ..

[查看全文]

FPGA有限状态机模拟I2C总线设计

2012-06-02

潘小冬

18

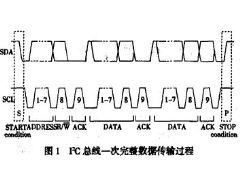

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模 ..

[查看全文]

ModelSim作布局布线后仿真的库问题

2012-06-02

13

Modelsim是目前最流行的应用最广泛的FPGA仿真器,是Mentor Graphics的子公司Model Technology开发的。因为Modelsim好学易用,调试方便,仿真速度快,功能强大,所以很多芯片厂商的开发系统都OEM Mentor Graphics公司的Modelsim仿真器,包括Xilinx,Altera,Lattice和Actel等。Modelsim是一个单内核仿真器,同一个内 ..

[查看全文]

FPGA与DS18B20型温度传感器通信的实现

2012-06-02

李农

14

摘要:介绍利用ACTEL公司的APA150型现场可编程门阵列(FPGA)实现对DS18B20型温度传感器的通信控制,使CPU可以方便地从FPGA中读取温度测量结果和DS18B20的48位ID值。 1 引言 DS18B20是DALLAS公司生产的一线式数字温度传感器,采用3引脚TO-92型小体积封装;温度测量范围为-55℃~+125℃,可编程为9位~12位A/D转 ..

[查看全文]

高速FPGA系统的信号完整性测试和分析

2012-06-02

张楷

50

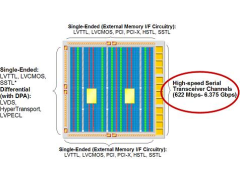

1. 引言 随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。典型的高速FPGA器件提供的每一条物 ..

[查看全文]

使用基于FPGA的硬件方法实现算法加速

2012-06-02

Lara Simsic

13

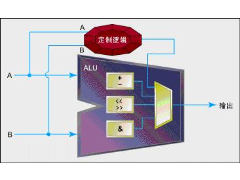

当设计者试图从算法中获得最佳性能但软件方法已无计可施时,可以尝试通过硬件/软件重新划分来进行加速。FPGA易于实现软件模块和硬件模块的相互交换,且不必改变处理器或进行板级变动。本文阐述如何用FPGA来实现算法的硬件加速。 如果想从代码中获得最佳性能,方法包括优化算法、使用查找表而不是算法、将一切都转换为本地 ..

[查看全文]

modelsim仿真问题

2012-06-02

86

近段时间比较忙,尝试着将工作中碰到的问题记录下来,也许它在某一天它会变成一笔财富了?不管怎么说,尝试记录工作的点滴都是一个不错的点子,呵呵。夸奖一下我自己! 在用modelsim 6.0 se作仿真的时候碰到一个错误,在xilinx的数据库里面发现原因如下: Problem Description: Keywords: ModelSim, MXE, MTI, error, VSIM ..

[查看全文]

modelsim for linux安装指南

2012-06-02

22

for modelsim: 1 下载modelsim for linux的下载文件。应该总共有三个文件,分别是base,docs和linux.exe。都是gz压缩的。 2 解压缩linux.exe,解出来的是可以在终端中直接运行的文件,运行之,并安装。 3 分别解压base和docs在同一目录下。 4 把这时候的modeltech目录(也就是解压缩和安装后形成的目录)移动到你希望程序所存放 ..

[查看全文]

基于 Modelsim FLI 接口的FPGA仿真技术

2012-06-02

胡军强 李津生 洪佩琳

8

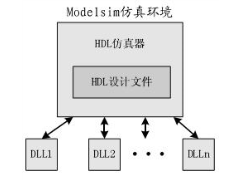

摘要:本文介绍了如何利用modelsim提供的FLI(Foreign Language Interface)接口进行VHDL设计文件的协同仿真,给出了协同仿真的意义以及协同仿真的程序结构和系统结构。 关键词:FPGA,仿真软件,协同仿真 1、Modelsim 及 FLI接口介绍 Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述语言仿真 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310