基于EMP7128的数字式相位测量仪

2012-06-22

尹佳喜

14

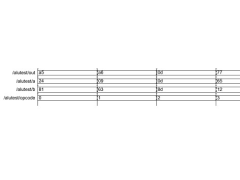

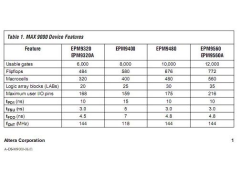

摘要:分析了基于Altera公司CPLD芯片EMP7128SLC84-15进行相位测量的基本原理,给出了用EMP7128SLC8415进行相位测量的硬件实现电路及VHDL源程序。 1 器件简介 EMP7128SLC84-15是Altera公司的MAX7000S系列CPLD,它采用CMOS工艺,并以第二代矩阵结构为基础,实际上也是一种基于E2PROM的器件。EM ..

[查看全文]

CPLD打乒乓球游戏电路仿真设计

2012-06-22

12

一、 实验目的(1) 学习用MAX+Plus II开发系统对可编程逻辑器件编程的方法;(2) 学习“CPLD/FPGA数字发展实验箱”的使用方法以及把文件下载到CPLD芯片中的方法。二、 仿真电路设计及设计思路仿真电路图如图所示。具体的电路接法及工作原理说明如下:用两个74LS194四位双向移位寄存器模拟乒乓球台,其中第一个74LS19 ..

[查看全文]

Synopsys软件介绍

2012-06-19

41

VCS VCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off的要求。VCS结合了节拍式算法和事件驱动算法,具有高性能、大规模和高精度的特点,适用于从行为级、 ..

[查看全文]

自动售货机控制系统VHDL有限状态机实现

2012-06-13

赖义汉

12

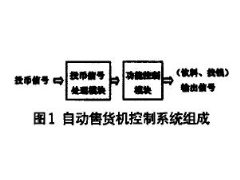

1 引言 有限状态机FSM(Finite State Machine)及其设计技术是实用数字系统设计中实现高效率、高可靠逻辑控制的重要途径。传统的状态机设计方法需进行繁琐的状态分配、绘制状态表、化简次态方程等,而利用VHDL可以避免这些繁琐的过程,直接利用状态转换图进行状态机的描述,所有的状态均可表达为CASE_WHEN结构中的一条CA ..

[查看全文]

Verilog HDL设计练习进阶(五)

2012-06-11

12

练习五. 用always块实现较复杂的组合逻辑电路 目的: 1.掌握用always实现组合逻辑电路的方法; 2.了解assign与always两种组合逻辑电路实现方法之间的区别。 仅使用assign结构来实现组合逻辑电路,在设计中会发现很多地方会显得冗长且效率低下。而适当地采用always来设计组合逻辑,往往会更具实效。已进行的范例和练习中,我们 ..

[查看全文]

VHDL 编程的一些心得体会

2012-06-02

6

VHDL 是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。 与另外一门硬件描述语言 Verilog HDL 相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且 VHDL 具有设计重用、大型设计能力、 ..

[查看全文]

VHDL的CRC编码器的设计

2012-06-02

郑春来

32

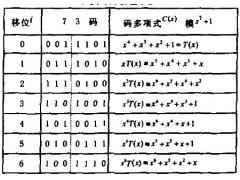

CRC码是线性分组码的一个重要子集,它是为了保证通信系统中的数据传输可靠性而采取的信道编码技术。CRC码除了具有分组码的线性外,还具有循环性,其码字结构一般用符号(n,k)表示,其中,n是该码组中的码元数,k是信息码位数,r=n-k是监督码元位数。循环码具有许多特殊的代数性质,这些性质有助于按照要求的纠错能力系统地 ..

[查看全文]

提高NC-Verilog仿真效率的技巧

2012-06-02

13

本文回顾了一些NC-Verilog的命令行选项,并说明这些选项如何影响仿真效率。同时,我们也展示了一些技巧,以帮助用户的NC-Verilog在最大效率下仿真一个设计和测试平台。 文中的命令行选项语法采用单步启动的方式(ncverilog +),这些选项也适合多步启动模式(ncvlog, ncelab, 或ncsim)。 安装最新发布的软件 首先确认你是否安 ..

[查看全文]

VHDL设计中的电路简化问题

2012-06-02

12

摘 要 :从描述方法、设计规则、逻辑函数分析了VHDL设计中容易引起电路复杂化的原因,并提出了相应的解决方法。 近年来,随着集成电路技术的发展,用传统的方法进行芯片或系统设计已不能满足要求,迫切需要提高设计效率。在这样的技术背景下,能大大降低设计难度的VHDL设计方法正越来越广泛地被采用。但是VHDL设计是行为级 ..

[查看全文]

修改D1N4002的仿真参数(PSpice)

2012-06-02

10

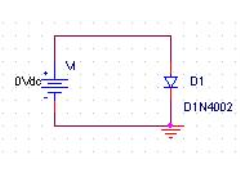

步骤一 绘出电路图、设置分析参数、存档及执行仿真 1、半导体元件均有其对应的仿真模型,所以我们可以根据自己的需求更改其模型型参数,以产生一个与元件有不一 样输入输出特性的二极管。首先新开一个项目D1N4002_1,然后如图1绘制电路图(也可以由D1N4002绘图页内复制 过来)。 图1 测量二极管V-I特性曲线的电路 2、然后用鼠 ..

[查看全文]

FPGA三国志-第二篇/结构篇

2012-06-02

wisdomz

8

Altera FPGA的速度没有Xilinx的速度快,错!当然这种非对称的结构,你必须有一定的了解,才可以更好的利用.也就是要遵循: 大的数据吞吐通道应该采用横向放置规划! 控制通路采用纵向放置规划! Altera至此以后,一直沿袭这种结构规划.因此,如果你想有效利用好Altera的产品,就应该遵守这个规则.但是要说明的,真正能体现性能的东西,也许 ..

[查看全文]

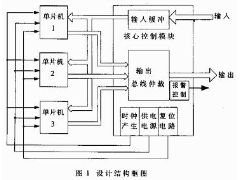

单片机多机冗余设计及控制模块的VHDL语言描述

2012-06-02

刘先昆 潘红兵

13

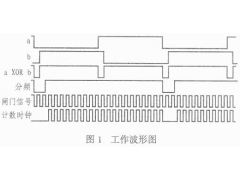

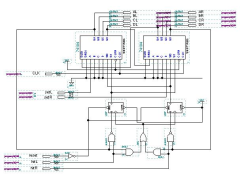

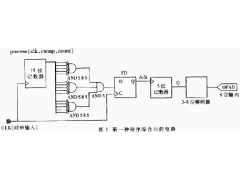

摘要:以三个单片机组成的系统为例介绍一种单片机多机冗余容错设计。阐述设计中关键的时钟同步技术和总线仲裁方法,给出控制模块的VHDL语言描述。 本文提出一种表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复杂的机间通讯协议实现系统重构,不太注重系统的实时性。本方 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310