基于VHDL的串口通信程序

2012-11-23

16

-- 本模块的功能是验证实现和PC机进行基本的串口通信的功能。需要在 --PC机上安装一个串口调试工具来验证程序的功能。 -- 程序实现了一个收发一帧10个bit(即无奇偶校验位)的串口控 --制器,10个bit是1位起始位,8个数据位,1个结束 --位。串口的波特律由程序中定义的div_par参数决定,更改该参数可以实 --现相应的波特率。程 ..

[查看全文]

一种基于FPGA的并行流水线FIR滤波器结构

2012-11-23

王黎明 刘贵忠 刘龙 刘洁瑜

26

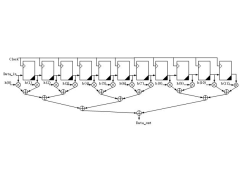

摘要: 本文提出一种在FPGA器件上实现流水线并行FIR滤波器结构。首先比较了FIR滤波器三种硬件实现所用的资源,然后在理论上推出本文流水线并行结构滤波器的实现方法以及可行性,接着给出了硬件具体实现模块,最后给出了实验结果。实验结果可以看出,这种改进滤波器实现结构的算法可以灵活的处理综合的面积和速度的约束关系, ..

[查看全文]

SDRAM控制器软核的Verilog设计

2012-11-23

20

目前,在很多通信芯片及系统的开发中,常常需要用到存储容量大、读写速度高的存储器。在各种随机存储器件中,SDRAM 的价格低、体积小、速度快、容量大,是比较理想的器件。但是,与SRAM相比较,SDRAM的控制逻辑复杂,使用很不方便。为了解决这个矛盾,需要设计专用的SDRAM控制器,使系统用户象使用SRAM一样方便的使 ..

[查看全文]

FPGA控制远程控制伺服马达

2012-11-21

12

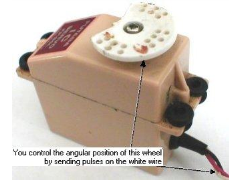

远程控制伺服马达 FPGA也适合用来控制“远程控制伺服马达”( R/C Servos) 什么是远程伺服马达? “远程控制伺服马达”由有电动机和一系列安装在盒子里的齿轮组成。此设备有一根转动轴,你可以通过使用PWM(脉宽调制)脉冲来精确控制它的转向。下面是一副它的图片(虽然又旧又破,但是完成了我们的设 ..

[查看全文]

FPGA/CPLD实验教程四(基本的逻辑门实验)

2012-11-19

抽烟的鱼

30

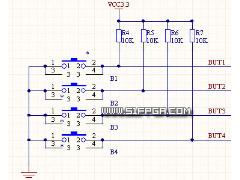

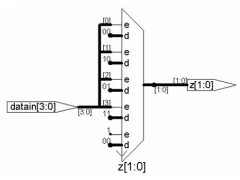

1. 实验要求及目的: 前面三个实验我们都只用到了LED,也就是输出。但是我们做的东西多半都是需要人机交互的,所以不能光是有输出,还应该有输入(其实前面也用到了输入,那就是时钟)。这个实验我们会用到按钮,通过按钮输入,判断逻辑,然后利用LED来显示出来逻辑输出结果。 这个实验主要是体会一下输入的用法,难度比较小 ..

[查看全文]

多途径降低FPGA设计的功耗

2012-11-19

10

每一代新的FPGA都变得速度更快、密度更高及规模更大。那么要怎么做才能确保功耗不同时增加呢?许多设计抉择,从明显的器件选择到更细微的状态机值选择等,都会对系统功耗构成影响。 为了更好地理解本文所要讨论的设计技巧如何能节省功耗,让我们先对功耗做一个简要介绍。 功耗包含两部分:动态功耗与静态功耗。动态功耗是指对 ..

[查看全文]

综合中的Metalogical Value

2012-11-17

峻少

7

Metalogical value是指: don't care, unknown和high-impedance这三个值。 我们对这几个 meta-logic 关心的主要有几个问题: 能否与其他信号或者变量进行比较? 能否赋值给其他信号或者变量? 1.Don't-Care 在综合的时候,含有“-”,或者“D”, “X”这类表示don’t-care的值是无法 ..

[查看全文]

基于FPGA/CPLD和USB技术的无损图像采集卡

2012-11-16

姚聪

28

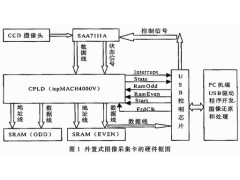

现场图像采集技术发展迅速,各种基于ISA、PCI等总线的图像采集卡已经相当成熟,结合课题设计了一款USB外置式图像采集卡。该图像采集卡已成功应用于一个图像处理和识别的项目中,由于图像信号不经过压缩处理,对后续处理没有任何影响,因此图像处理和识别的效果比一般的图像采集卡要好,满足了特殊场合的特殊需要。 1 外置式 ..

[查看全文]

NIOS整体开发结构基础

2012-11-14

15

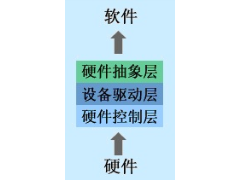

上个例子中,我们使用VHDL语言,根据FPGA管脚与数码管和按键管脚的连接,通过一系列的语句控制管脚电平的高低,从而让FPGA实现数码管显示功能。可见,对于比较简单的功能实现,可以像这个例子中那样,直接控制最底层资源,甚至对每个管脚在每个时刻的电平输出了如指掌。 但是,如果设计稍显复杂,那么对底层细节的过多关注 ..

[查看全文]

verilog HDL 的阻塞和非阻塞语句分析

2012-11-14

e人

13

在FPGA设计中完全透视verilog HDL 的阻塞和非阻塞语句,是个人在verilog HDL运用中的一些心得体会。 阻塞和非阻塞语句作为verilog HDL语言的最大难点之一,一直困扰着FPGA设计者,即使是一个颇富经验的设计工程师,也很容易在这个点上犯下一些不必要的错误。阻塞和非阻塞可以说是血脉相连,但是又有着本质的差别。理解不清 ..

[查看全文]

Quartus II与 ModelSim功能仿真与后仿真扫盲

2012-11-13

yangyh80@21cn.com

34

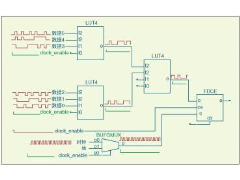

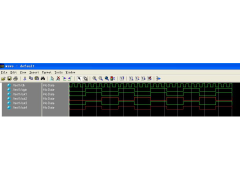

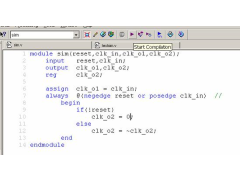

本文主要描述了如何在QUARTUS II 中输入程序文件,生成网表及标准延时文件,然后通过MODELSIM 进行功能仿真与后仿真的过程,主要为图解,含全部代码及仿真波形。 工具: Quartus II 5.0 sp1 ModelSim SE 6.1b 芯片:MAX II :EMP570T100I5 语言:Verilog HDL 程序功能:太简单了,自己看源程序吧 源程序: module sim(reset ..

[查看全文]

How to quickly use ModelSim Coverage in Simulation

2012-11-12

Xiao Jie

11

1. Star ModelSim and Make filelist Star your modelsim and change the directoryto youre project folder. Use “pwd “to show your current directory. Use “cd d:\verilog“to change directory. Use “dir *.v /b/s >filelist.f “ to make file list. The file list is as follow, which con ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310