Verilog HDL设计练习进阶(十)

2012-12-20

8

练习十. 通过模块之间的调用实现自顶向下的设计 目的:学习状态机的嵌套使用实现层次化、结构化设计。 现代硬件系统的设计过程与软件系统的开发相似,设计一个大规模的集成电路的往往由模块多层次的引用和组合构成。层次化、结构化的设计过程,能使复杂的系统容易控制和调试。 在Verilog HDL中,上层模块引用下层模块与C语言中 ..

[查看全文]

让ISE8.1和ISE8.2的库共存于ModelSim6.0

2012-12-17

14

(包含SmartModel) 第一次compxlib - ISE8.1 1. 设置好XILINX环境变量:XILINX=D:ISE81 2. 设置好LMC_HOME环境变量: LMC_HOME=D:XilinxLibmti_pesmartmodel81 3. 确认modelsim.ini的读写状态(只读的话compxlib将新建一个modelsim.ini于当前工作目录)- 设为只读 3. 使用Compxlib: compxlib -s mti_pe -arch all -lib ..

[查看全文]

Debussy仿真快速上手教程

2012-12-17

52

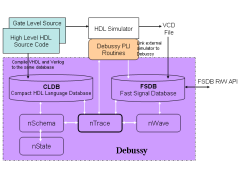

Debussy 介绍 Debussy 是NOVAS Software, Inc(思源科技)发展的HDL Debug & Analysis tool,这套软体主要不是用来跑模拟或看波形,它最强大的功能是:能够在HDL source code、schematic diagram、waveform、state bubble diagram之间,即时做trace,协助工程师debug。 可能您会觉的:只要有simulator如ModelSim ..

[查看全文]

并串转换之VHDL 源程序

2012-12-16

8

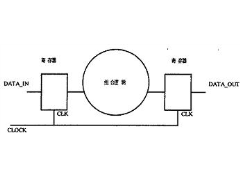

昨天在论坛上看到有人帖出了他写的并串转换VHDL代码,但是他自己说有问题,但是不知道怎么改。我大概看了一下,发现思路还是比较乱的。于是就写下了我自己的并串转换代码。这个并串转换代码是依靠同步状态机来实现其控制的。其实并串转换在实际的电路中使用还是比较多的,尤其在通信线路方面的复用和分解方面,原理上就是一 ..

[查看全文]

FPGA 多时钟设计

2012-12-16

Tim Behne

7

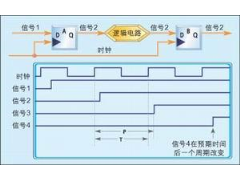

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。 FPGA设计的第一步是决定需要 ..

[查看全文]

FPGA的VHDL设计策略

2012-12-15

罗旻 沈绪榜 高德远

13

1 概述 目前, 可编程逻辑器件(PLD) 的密度、速度和I/O 接口已经可以满足大多数的数字ASIC 的设计要求, 因而得到了越来越广泛的使用. 同时, 所涉及的门数已经从几百门增加到几十万门, 使得原先设计所使用的逻辑图输入、真值表和卡诺图的设计方法已经远远不能满足数字系统的复杂性要求. 采用硬件描述语言(Hardware Descriptio ..

[查看全文]

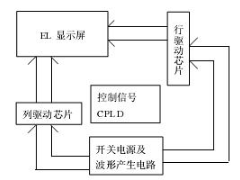

CPLD、FPGA 在 EL 显示模块及接口电路中的应用

2012-12-15

李 春 廖建勇 柴天恩

14

摘要 :在 EL 显示模块中,采用 CPLD 芯片可以实现数字电路的集成。这种方法有利于缩小模块体积,加快开发速度,提高模块电路的稳定性。在相关的接口电路中,采用 FPGA替代液晶显示器专用控制芯片,实现 EL 模块所需的接口时序及数据格式。这种方法具有较强的实用性及可升级性。 关键词 :复杂可编程逻辑器件(CPLD) ; 现场可编程逻辑 ..

[查看全文]

用Verilog-HDL做CPLD设计(目标板的设计和下载软件的使用)

2012-12-15

李媛媛 常晓明

9

Verilog-HDL与CPLD/FPGA设计应用讲座 第 6讲 用Verilog-HDL做CPLD设计 目标板的设计和下载软件的使用 6.1 目标板的制作 6.2 一个最简单的设计 6.3 一个最简单设计的实现--下载实例 6.1 目标板的制作 学习了Verilog-HDL的基本概念,并用其仿真环境Modelsim XE对基本逻辑电路进行仿真后,如果希望在硬件上实现所设计的电路功能 ..

[查看全文]

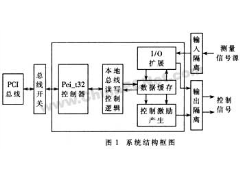

基于IP核的PCI总线接口设计与实现

2012-12-12

刘红,李勃,常青,吴鑫山

19

PCI总线是高性能的32/64位同步总线,具有严格的规范保证数据传输的可靠性,微处理器与高集成度的外围设备提供高速安全的接口,是迄今为止最成功的总线规范之一。 由于PCI总线协议非常复杂,目前实现PCI总线接口主要是使用两种方式:(1)采用专用接口芯片,如AMCC公司的S5933和PLX公司的9054、 9080。使用接口芯片开发 ..

[查看全文]

Nios II IDE软件编译环境探密

2012-12-12

16

Nios II IDE编译环境提供了许多工程模板帮助用户尽可能的快速的推出可运行的系统,可是当我们用一种模板生成应用环境后,需要增加其他应用模式的时候就会遇到问题,我们有必要对Nios II IDE的编译环境有一个了解,使我们灵活的去配置编译系统,下面介绍的内容对于熟悉LINUX系统编程的开发者可能很熟悉,希望我们一起来分析Nio ..

[查看全文]

在Nios II 7.2中打开MMU功能的方法

2012-12-11

骏龙科技

12

按住你键盘上的“ctrl”键后选择你的CPU,然后在SOPC Builder 点击“edit”。 这时出现了一个新的窗口。选中“setting_ShowUnpublishedSetting”选项,这样CPU Core 选项窗口中就出现了MMU 选项。 注意:Linux 版本暂时不提供NIOS II MMU 功能。 以下图片就是具体步骤(点击图片查看大图) ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310