PCI总线是高性能的32/64位同步总线,具有严格的规范保证数据传输的可靠性,微处理器与高集成度的外围设备提供高速安全的接口,是迄今为止最成功的总线规范之一。

由于PCI总线协议非常复杂,目前实现PCI总线接口主要是使用两种方式:(1)采用专用接口芯片,如AMCC公司的S5933和PLX公司的9054、 9080。使用接口芯片开发人员可以不考虑PCI接口的实现问题,但是在实际应用中通常只用到接口芯片的部分功能,造成了资源的浪费,同时接口芯片占用了板卡上的有限空间,给应用设计带来不便。(2)使用可编程逻辑器件实现PCI总线控制器,使用这种方式开发难度大,消耗周期长,系统验证困难,且不具备通用性。随着IC产业的迅速发展,传统的、基于标准单元的数字IC设计方法已经发展到基于IP(知识产权)复用的SoC设计方法,根据实现的硬件描述级的不同, IP核分为软核、硬核和固核。其中,软核是采用可综合的HDL实现的RTL级设计,与具体实现工艺无关,相比于固核和硬核具有较大的灵活性,在FPGA中定制PCI接口软核实现PCI接口控制具有明显的优势:可以在单片FPGA中同时完成PCI接口和用户逻辑的设计,缩减成本,提高集成度,减少资源浪费,实现32/64位的PCI、PCI-X及兼容Compact PCI的PCI主设备/目标设备接口,消除PCI接口芯片与本地通信的信号线的硬线连接,提高用户逻辑设计的弹性,降低因硬件设计不当造成的损失;统一设计工具和平台,缩短开发周期。

本文应用PCI接口控制IP实现了PCI多卡测控系统中PCI总线到本地总线的转换,实际应用表明,采用此设计方案的PCI卡运行稳定可靠。

1 应用背景

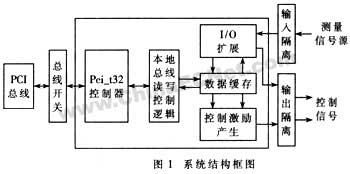

本文的应用背景为某一工业测控系统,该系统采用FPGA实现测量数据的采集和控制信号的输出,通过定制PCI接口IP实现一个32位目标设备的PCI总线接口转换。PCI核选用Altera PCI编译器所包括的pei_t32兆核函数,FPGA选用Altera公司的Cyclone系列芯片eplc6q240c8,以配合32位/33MHz 的PCI接口的I/O标准和速度要求,在硬件设计上,为保证3.3V FPGA对PCI 2.2、5V总线的兼容性要求,在PCI总线接口与FPGA引脚间加入总线开关进行电平转换。由于系统应用在工业生产控制场合,因此FPGA与外部数据的 I/O接口间需要加入光电隔离器件以增量系统的抗干扰能力,系统结构如图1所示。

|

|

2 PCI接口兆核函数

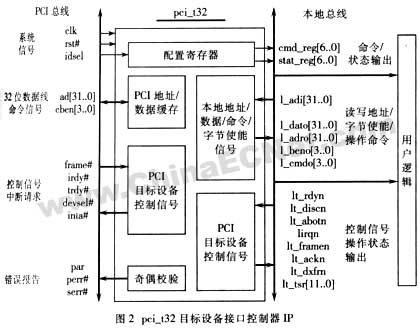

Altera的PCI编译器(PCI Compiler)提供了使用Altera器件实现PCI接口设计的完全解决方案,包括4个32/64位、主/从模式PCI接口控制器兆核函数(即接口 IP)及相关测试平台,通过选择合适的芯片速度,可以满足运行在33MHz或66MHz PCI时钟下的时序要求,支持Altera的Stratix II、Stratix、Stratix GX、Cyclone、Cyclone II和MAX II系列器件,支持PCI配置空间读写、内存方式读写和I/O方式读写,支持预先读取模式,支持可参数化的配置寄存器,包括参数化的设备信息、6个可变长度的基址空间和一个扩展ROM空间,具有奇偶校验检错,支持PCI终止、重试和断开作业及中断操作,并提供灵活的本地端接口,pci_t32兆核函数的 32位目标设备控制器,其结构和总线接口信号如图2所示。

|

|

在PCI总线端,IP核提供32位数据线和目标设备控制信号、中断请求信号及错误报告信号,本地总线端提供32位数据线和地址线、控制信号、中断输入信号和状态表示信号接口。其中,本地端信号L_adi为地址/数据输入,l_adro为地址输出,l_dato为数据输出,L_beno为字节使能输出,l_cmdo为本地命令输出。控制信号lt_abortn、lt_discn和lt_rdyn为本地端输入,分别标志本地设备终止、断开和准确好、lt_framen、lt_ackn和lt_dxfrn为目标传输控制信号,相当于PCI总线的frame#、devsel#和trdy#。 lt_tsr为目标作业状态寄存器输出。lirqn为中断输入信号。

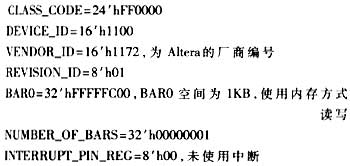

可以通过PCI编译器IP工具台或编辑兆核函数头文件的方式修改PCI配置空间信息,本系统GCI兆核函数的配置信息如下:

|

|

3 本地总线读写状态机

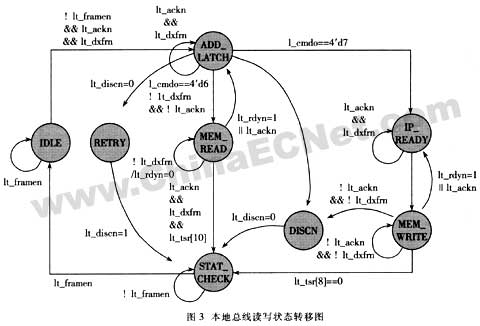

在用户逻辑中,通过总线读写状态机实现内存方式单周期或迸发读写、I/O单周期或迸发读写以及在设备不能完成作业时发起(目标)或响应(主)终止、断开或重试等作业,保证PCI作业正确结束,以带迸发模式的内存读写作业为例,作为目标设备的本地总线读写状态转移图如图3所示。

|

|

IDLE为设备空闲状态。

ADD_LATCH为地址锁定状态。lt_framen有效表示IP核接到一次PCI读写作业并启动本地端做出响应,此时目标设备锁存地址l_adro及命令L_cmdo,并对命令做出解释。l_cmdo的值为6,则进入MEMORY_READ状态;为7,则进入IP_READY状态;其他值,则使能lt_discn并进入RETRY状态。

MEM_READ为内存读作业状态, lt_ackn有效驱动目标设备将数据放到总线上,如为迸发方式,则lt_rdyn和lt_dxfrn持续有效,驱使目标设备连续将地址相连的数据输出,如目标设备在迸发作业中需延缓迸发作业,则可使lt_rdyn无效来进入等待周期,此时状态机回到ADD_Latch状态,直到目标设备再次准备好,并同时使lt_rdyn有效并输出数据。

RETRY为设备重试状态,在作业开始,目标设备尚未准备好发送或接收数据,则发起一次重试作业,即在lt_framen有效后使lt_discn有效并等待主设备结束作业。

DISCN为设备断开状态,在迸发读写左右中,目标设备检测到地址超出有效范围,则发起目标断开作业,在迸发写作业中断,在最后一次有效写数据前一时钟使lt_discn有效,在迸发读作业中,将最后一个数据放在总线上的同时使Lt_discn有效。

IP_ready为内存写操作IP核准备传输数据状态。

MEM_WRITE为内存写作业状态,在同时使能lt_rdyn后等待lt_ackn和lt_dxfrn有效时读取总线上的数据l_dato,迸发写或加入等待周期的时序与读作业类似。

STAT_CHECH为状态检测;lt_ackn和lt_dxfrn同时无效标志着内存单次/迸发读作业完成,然后检测作业状态寄存器Lt_tsr并返回IDLE状态。

每一次作业开始,都启动计数器,防止操作超时。

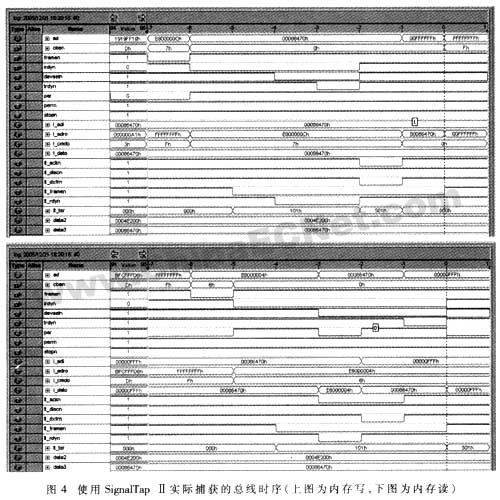

使用SignalTap II嵌入式逻辑分析仪实际捕获的PCI内存读写作业的PCI和本地总线信号时序图如图4所示,采样时钟为PCI总线时钟。

|

|

4 PCI电气特性要求设计

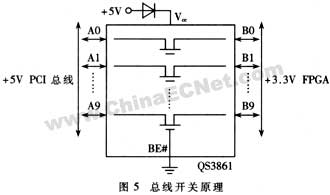

由于目前绝大多数主板采用5V的PCI规范,而Altera的Cyclone系列FPGA的I/O口电压只支持3.3V,因此需要在FPGA和PCI连接器间加入电平转换电路。

实现电平转换的原理是在总线间加入NMOS总线开关,实现方式如图5所示。

|

|

其中总线开关选用IDT公司的QS3861,首先,考虑电平转换的实现方法,当总线选通信号BE#使能,总线A的输入电压上升,总线B的电压随之上升,当总线A的电压超过Vcc-Vt(Vt的典型值为1V)时,总线B的电压将被箝位到Vcc-Vt,而不会继续上升,因此选择Vcc位4.3V,则能保证总线B的信号满足3.3V标准。当3.3V总线B驱动总线A时,由于5V PCI规范中定义的逻辑高电压是2V-5.5V,因此也能够保证FPGA端驱动PCI的高电压要求。其次,验证是否满足PCI时序要求,PCI2.2协议规定一个时钟周期分为4部分:

t(30ns)=tval+tprop+tsu+tskew

其中:tval为时钟到输出信号有效延迟,tsu为输入建立时间,tpro为最大总线传输时间,tskew为时钟抖动时间。PCI 2.2协议规定的保持时间为0。

tprop 是由于PCI总线采用反射波技术引入的,典型值为10ns,tprop与tskew的和不超过12ns。PCI 2.2规范规定33MHz信号的建立时间为7ns,66MHz信号的建立时间为3ns,由QS3861引入的数据传输延迟为0.25ns。但由于所有 PCI信号都经过总线开关进行电平转换,到达FPGA的信号整体只有0.25ns的延迟,因此FPGA的建立时间仍然设置为7ns,FPGA经过运算输出的信号时序由时钟到信号有效延迟tval所限定。PCI 2.2规范规定33MHz时tval最大为11ns,最小为2ns,由于电平转换芯片在双向数据通路的延迟累加,FPGA必须包括时钟到信号最大延迟在 10.5ns以内。

最后,考虑布局布线因素,在加入总线开关后,要保证从PCI连接器到总线开关及总线开关到FPGA的所有32位信号线(除中断输入信号、系统信号和JTAG信号)的走线长度和不大于1.5英寸、时钟线长度和为2.5±0.1英寸。

FPGA 中定制IP核实现PCI总线到本地总线的转换,能够有效节约PCI设备的成本,提高硬件资源利用率,缩短开发时间,目标设备读写状态机对本地总线进行监测,完成设备的内存、I/O读写并提供迸发作业支持,在发生异常状况时,及时发起重试,断开或终止作业,保证PCI总线传输正确结束,防止不安全的数据操作出现,为了满足PCI电气规范,在硬件设计时需要注意3.3V设备挂接5V总线的电平转换及其带来的时序和布线问题。

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 192

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261