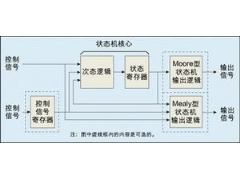

高速环境下的状态机设计策略

2012-11-10

14

通过减少寄存器间的逻辑延时来提高工作频率,或通过流水线设计来优化数据处理时的数据通路来满足高速环境下FPGA或CPLD中的状态机设计要求。本文给出了采用这些技术的高速环境状态机设计的规范及分析方法和优化方法,并给出了相应的示例。 为了使FPGA或CPLD中的状态机设计满足高速环境要求,设计工程师需要认识到以下几点 ..

[查看全文]

Verilog HDL设计练习进阶(四)

2012-11-08

8

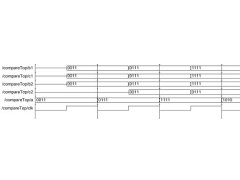

练习四. 设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别 目的:1.明确掌握阻塞赋值与非阻塞赋值的概念和区别; 2.了解阻塞赋值的使用情况。 阻塞赋值与非阻塞赋值,在教材中我们已经了解了它们之间在语法上的区别以及综合后所得到的电路结构上的区别。在always块中,阻塞赋值可以理解为赋值语句是顺序执行的,而非阻塞赋值可以 ..

[查看全文]

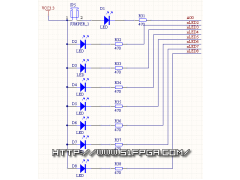

FPGA/CPLD实验教程三(流水灯)

2012-11-07

抽烟的鱼

152

1. 实验要求及目的: 这次的实验我们要做的是流水灯,顾名思义就是要LED象水一样的点亮(好像有点不怎么顾名思义啊),这样说吧,就是先单独点亮第一个,然后点亮第二个(这个时候有两个灯亮了),然后…… 这一个实验主要教会大家一个比较方便的锁定引脚的办法,另外就是使用移位运算符。 使用软件:Quartus II 5.0 ..

[查看全文]

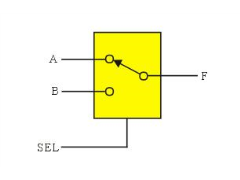

典型逻辑电路的Verilog-HDL描述

2012-11-06

常晓明 李媛媛

11

Verilog-HDL与CPLD/FPGA设计应用讲座 第 5 讲 典型基本逻辑路的Verilog-HDL描述 5.1 数据选择器 5.2 编码器 5.3 同步RS触发器 5.4 带有复位端的同步D触发器 本讲列举几个典型又简单的基本逻辑电路的Verilog-HDL描述。需要说明,仅有本讲的知识还不能具备用Verilog-HDL描述逻辑电路和系统的基本功,但却可以通过几个例子了解 ..

[查看全文]

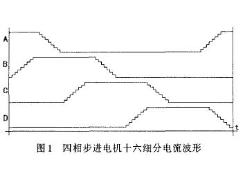

基于FPGA实现的步进电机细分控制信号发生器的设计

2012-11-06

郭改枝 李树华 俞宗佐

39

步进电机响应速度快、定位精度高、无积累误差、驱动电路及控制方法简单,在工业控制领域获得了广泛应用.但由于转动不够平稳,运行时会发生震荡现象,对系统的正常运行会产生不良影响,目前普遍认为最有效的解决方法是细分法.常用的细分法是用单片机实现或将细分参数存在EPROM 类非易失性存储器中通过逻辑电路实现细分输出 ..

[查看全文]

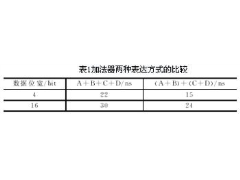

VHDL设计中电路优化问题

2012-11-06

王春玲

12

近年来,随着集成电路技术和EDA技术的不断发展,集设计、模拟、综合和测试功能为一体的VHDL语言,已作为IEEE标准化的硬件描述语言。由于其在语法和风格上类似于现代高级汇编语言,具有良好的可读性,描述能力强,设计方法灵活,易于修改,又具有可移植性,可重复利用他人的IP模块 (具有知识产权的功能模块)等诸多优势而成为 ..

[查看全文]

VHDL设计中电路简化问题的探讨

2012-11-05

14

近年来,随着集成电路技术的发展,用传统的方法进行芯片或系统设计已不能满足要求,迫切需要提高设计效率。在这样的技术背景下,能大大降低设计难度的VHDL设计方法正越来越广泛地被采用。但是VHDL设计是行为级的设计?熕?带来的问题是设计者的设计思考与电路结构相脱节。设计者主要是根据VHDL的语法规则对系统目标的逻辑行 ..

[查看全文]

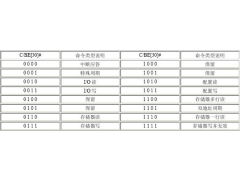

基于CPLD的单片机PCI接口设计

2012-11-05

吕 刚 周爱国

15

摘要:详细阐述一种利用CPLD 实现的8 位单片机与PCI 设备间的通信接口方案,给出用ABEL HDL 编写的主要源程序。该方案在实践中检验通过。 关键词:单片机 CPLD PCI 8 位单片机在嵌入式系统中应用广泛,然而让它直接与PCI 总线设备打交道却有其固有缺陷。8 位单片机只有16 位地址线,8 位数据端口,而PCI 总线2.0 规范中,除了 ..

[查看全文]

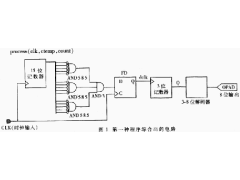

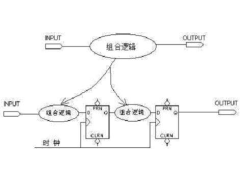

如何拆分大的组合逻辑?

2012-11-05

12

lflhust: 图1是很多为了提高系统时钟采用的拆分大组合逻辑的方法,但是没有提供具体如何拆分的实例。我觉得实例才是重要的。但我不明白在写代码时,如何知道这样写会被综合成一个很大的逻辑,一些简单的可以想到(比如大的计数器应该分成多个来做),但是更复杂的实在是不好理解。 图1 fpga521: 可以通过流水线的方式分拆组合逻 ..

[查看全文]

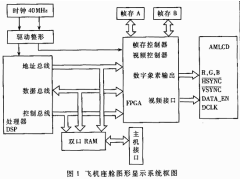

基于FPGA的LCD&VGA控制器设计

2012-11-03

朱耀东

19

飞机座舱图形显示系统已发展到第六代,即采用有源矩阵彩色液晶显示器AMLCD (Active Matrix Liquid Crystal Display)。当前高分辨率的军用AMLCD显示模块还只能依靠进口,且控制电路板须安装在该显示模块提供的机箱内。这种安装方式对AMLCD控制电路板的尺寸要求高,要求尽可能减少所设计电路板的尺寸。在笔者设计的新一 ..

[查看全文]

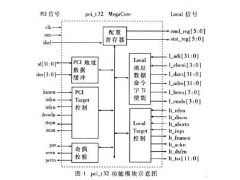

基于FPGA的PCI接口设计

2012-11-02

宋克柱 杨小军 王砚方

15

摘 要: 介绍一种使用PCI宏核逻辑进行的更加简单高效的PCI口设计方法。该方法将PCI接口和PCI用户逻辑集成在一片FPGA里,可以对整个逻辑进行仿真调试,大大缩短了开发周期、提高了系统集成度和性能。重点叙述了ALTERA公司提供的32位TAGET接口宏核pci_t32的原理和结构,分析了时序设计要点,给出了典型应用的逻辑设计框图 ..

[查看全文]

用VHDL语言设计延时电路

2012-11-02

21

用VHDL语言设计延时电路时一般用计数器或计数器的级联来实现。 下面以一个实例来说明如何实现任意时间量的延时。 在5 MHz时钟CLK控制下对同步信号SYNC进行N延时(SYNC脉冲宽度为2 μs,脉冲重复频率为1 kHz;0μs≤N≤998 μs)。要求每次在同步脉冲上升沿到来时开始延时,并在延时结束后产生宽度为10 μ ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310