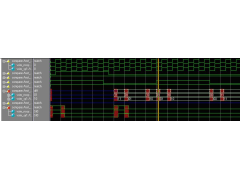

基于 Modelsim FLI 接口的FPGA仿真技术

2012-06-02

胡军强 李津生 洪佩琳

10

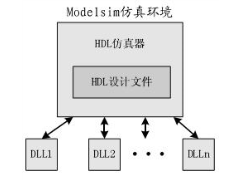

摘要:本文介绍了如何利用modelsim提供的FLI(Foreign Language Interface)接口进行VHDL设计文件的协同仿真,给出了协同仿真的意义以及协同仿真的程序结构和系统结构。 关键词:FPGA,仿真软件,协同仿真 1、Modelsim 及 FLI接口介绍 Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述语言仿真 ..

[查看全文]

基于Nios的DDS高精度信号源实现

2012-06-02

鲜华

18

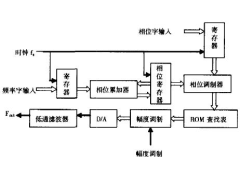

摘要:直接数字频率合成器DDS具有极高的分辨率、频率转换速度快、相位噪声低等优点。以ALTERA公司的CPU软核Nios为基础,利用Quartus II软件和Sopc Builder,采用两级DDS和动态分频法,提高了信号源的精度。采用双口ROM可以很方便的同时输出两路具有一定相位差的信号,而且频率幅度可调。另外着重介绍了怎样用Matlab产 ..

[查看全文]

基于单片机的复杂可编程逻辑器件快速配置方法

2012-06-02

16

基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存配置数据。这些配置数据决定了PLD内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。由于SRAM的数据是易失的,因此这些数据必须保存在PLD器件 ..

[查看全文]

Verilog HDL设计练习进阶(二)

2012-06-02

12

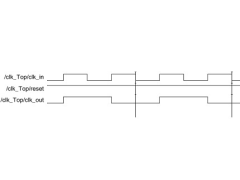

练习二. 简单时序逻辑电路的设计 目的:掌握基本时序逻辑电路的实现。 在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型,我们通常使用always块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个1/2分频器的可综合模型。 // half_clk.v: module half_clk( ..

[查看全文]

verilog HDL设计练习进阶(一)

2012-06-02

7

练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法。 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 模块源 ..

[查看全文]

怎样用modelsim做后仿真

2012-06-02

26

怎样用modelsim做后仿(编译工具采用quatus) step1: 在qurtus改变编译选项: assignments->EDA tool setting:选择verilog还是vhdl。 step2: 编译。你会在你的工程所在目录 看到一个simulation的目录,这里面有你生成的网表文件和标准延时文件。 step3: 在目录:\quartus\eda\sim_lib找到你选用器件对应的库文件,将库文件 ..

[查看全文]

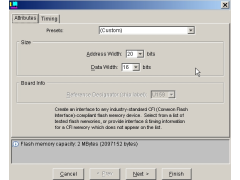

Nios II中Flash的使用

2012-06-02

12

在嵌入式系统中,Flash是最常用组件之一。许多使用过flash的朋友都了解,Flash的特点是“读来容易写来难”。通常,可以直接读出Flash的内容;但如果要写入数据,就要发送一长串命令,比如像:555 ,AA,2AA,55,555,A0 ,PA,PD就表示对PA地址写入数据PD,实际情况还要复杂一点,因为通常还要包含许多查询 ..

[查看全文]

modelsim for linux安装指南

2012-06-02

24

for modelsim: 1 下载modelsim for linux的下载文件。应该总共有三个文件,分别是base,docs和linux.exe。都是gz压缩的。 2 解压缩linux.exe,解出来的是可以在终端中直接运行的文件,运行之,并安装。 3 分别解压base和docs在同一目录下。 4 把这时候的modeltech目录(也就是解压缩和安装后形成的目录)移动到你希望程序所存放 ..

[查看全文]

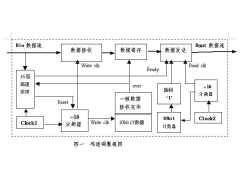

用FPGA实现非标码速向标准码速的调整

2012-06-02

33

摘要:本文主要讨论了如何利用FPGA可编程芯片实现计算机输出的异步非标码速(如9.6k、19.2k、57.6k、115.2k、460.8k等)到其邻近的标准码速(如64k、128k、256k、512k)的调整,实现该数据与通用传输系统的适配,以便能进行远程监控。 关键词:码速调整 FPGA 一、概述 现在,利用计算机进行异地数据采集正应用到越来越 ..

[查看全文]

奇数次分频器

2012-06-02

10

奇数次分频器 module count(out,clk,clr); parameter N=5; output out; input clk,clr; reg out1,out2; reg [N/2:0] count1,count2; always @(posedge clk or posedge clr ) if(clr) begin count1=0; out1=0; end elsebegin count1 = count1 + 1; if( count1 == ((N+1)/2)) out1 =!out1; else if (count1==N) begin out1=~out1; coun ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317