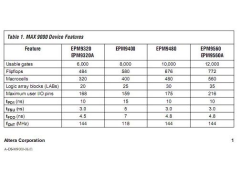

FPGA三国志-第二篇/结构篇

2012-06-02

wisdomz

9

Altera FPGA的速度没有Xilinx的速度快,错!当然这种非对称的结构,你必须有一定的了解,才可以更好的利用.也就是要遵循: 大的数据吞吐通道应该采用横向放置规划! 控制通路采用纵向放置规划! Altera至此以后,一直沿袭这种结构规划.因此,如果你想有效利用好Altera的产品,就应该遵守这个规则.但是要说明的,真正能体现性能的东西,也许 ..

[查看全文]

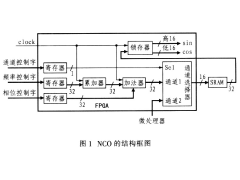

基于FPGA和SRAM的数控振荡器的设计与实现

2012-06-02

佟力永 肖山竹

12

1 、引言 数控振荡器是数字通讯中调制解调单元必不可少的部分,同时也是各种数字频率合成器和数字信号发生器的核心。随着数字通信技术的发展,对传送数据的精度和速率要求越来越高。如何得到可数控的高精度的高频载波信号是实现高速数字通信系统必须解决的问题,可编程逻辑器件和大容量存储器的发展为这一问题的解决带来了曙光 ..

[查看全文]

基于MATLAB和Quartus II的FIR滤波器设计与仿真

2012-06-02

张园 王辉

32

在现代数字系统中,FPGA(现场可编程门阵列)以计算机为开发平台,经过设计输入、仿真、测试和校验,直至达到预期结果。本文使用MathWorks公司的MATLAB软件和Altera公司的FPGA开发软件Quartus II进行FIR滤波器的设计仿真,并给出了设计的一般步骤。该方法能够直观地检验滤波器的设计效果,提高设计效率,缩短设计周期。 ..

[查看全文]

复用器重构降低FPGA成本

2012-06-02

13

摘要 本文介绍了一种新的能够降低FPGA实际设计20%成本的综合算法。该算法通过减少复用器所需查找表(LUT)的数量来实现。算法以效率更高的4:1复用器替代2:1复用器树。算法性能关键在于寻找总线上出现的复用器数量。新的优化方法占用一定的逻辑,这些逻辑由总线进行分担,从而减少了总线上每个比特位所需的逻辑。 1.引言 复 ..

[查看全文]

怎样用modelsim做后仿真

2012-06-02

26

怎样用modelsim做后仿(编译工具采用quatus) step1: 在qurtus改变编译选项: assignments->EDA tool setting:选择verilog还是vhdl。 step2: 编译。你会在你的工程所在目录 看到一个simulation的目录,这里面有你生成的网表文件和标准延时文件。 step3: 在目录:\quartus\eda\sim_lib找到你选用器件对应的库文件,将库文件 ..

[查看全文]

VHDL 编程的一些心得体会

2012-06-02

8

VHDL 是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。 与另外一门硬件描述语言 Verilog HDL 相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且 VHDL 具有设计重用、大型设计能力、 ..

[查看全文]

CPLD开发板和FPGA开发板的区别

2012-06-02

抽烟的鱼

21

市面上尤其是学校里面可以看到Xilinx公司或者Altera公司各种不同的开发板,其实只有两个大类,CPLD开发板和FPGA开发板。尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点: ①CPLD更适合完成各种组合逻辑,FPGA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富 ..

[查看全文]

基于VHDL的异步串行通信电路设计

2012-06-02

李刚强

21

1 引 言 随着电子技术的发展,现场可编程门阵列 FPGA和复杂可编程逻辑器件CPLD的出现,使得电子系统的设计者利用与器件相应的电子CAD软件,在实验室里就可以设计自己的专用集成电路ASIC器件。这种可编程ASIC不仅使设计的产品达到小型化、集成化和高可靠性,而且器件具有用户可编程特性,大大缩短了设计周期,减少了设计费 ..

[查看全文]

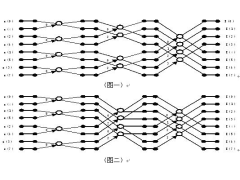

固定几何结构的FFT算法及其FPGA实现

2012-06-02

11

1.引言 DFT及其快速算法FFT是信号处理领域的核心组成部分。FFT算法多种多样,按数据组合方式不同一般分时域和频域,按数据抽取方式的不同又可分为基2,基4等。各算法的优缺点视不同的制约因素而不同。FFT的实现方法也多种多样,可以用软件实现,也可以用硬件实现,用软件在PC机或工作站上实现则计算速度很慢。一般多结合 ..

[查看全文]

半整数分频的VHDL程序

2012-06-02

12

想出了一个半整数分频的VHDL语言描述 其实很多问题只要你耐心,也是比较容易的 写出来与大家共享,共同讨论,半整数分频当然还有其他的方法 我认为这种看起来蛮简单的 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity abc is port(clk:in std_logic; dout:out std_logic); end abc; architecture x ..

[查看全文]

奇数次分频器

2012-06-02

10

奇数次分频器 module count(out,clk,clr); parameter N=5; output out; input clk,clr; reg out1,out2; reg [N/2:0] count1,count2; always @(posedge clk or posedge clr ) if(clr) begin count1=0; out1=0; end elsebegin count1 = count1 + 1; if( count1 == ((N+1)/2)) out1 =!out1; else if (count1==N) begin out1=~out1; coun ..

[查看全文]

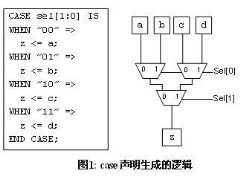

用Verilog-HDL做CPLD设计(组合逻辑电路的实现)

2012-06-02

李媛媛 常晓明

13

Verilog-HDL与CPLD/FPGA设计应用讲座 第 7 讲 用Verilog-HDL做CPLD设计 组合逻辑电路的实现 7.1 与非门的实现 7.2 2-1数据选择器的实现 7.3 2位二进制编码器的实现 7.4 1位数据比较器的实现 本讲中,我们通过由浅入深的实例来介绍组合逻辑电路在目标板上是如何实现的。 7.1 与非门的实现 首先,来实现一个用两个开关控制一个灯的 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317