Altera FPGA、CPLD 学习笔记

2012-06-02

11

1.硬件设计基本原则 速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用 & ..

[查看全文]

VHDL的CRC编码器的设计

2012-06-02

郑春来

39

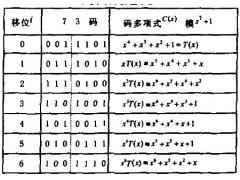

CRC码是线性分组码的一个重要子集,它是为了保证通信系统中的数据传输可靠性而采取的信道编码技术。CRC码除了具有分组码的线性外,还具有循环性,其码字结构一般用符号(n,k)表示,其中,n是该码组中的码元数,k是信息码位数,r=n-k是监督码元位数。循环码具有许多特殊的代数性质,这些性质有助于按照要求的纠错能力系统地 ..

[查看全文]

FPGA三国志-第二篇/结构篇

2012-06-02

wisdomz

9

Altera FPGA的速度没有Xilinx的速度快,错!当然这种非对称的结构,你必须有一定的了解,才可以更好的利用.也就是要遵循: 大的数据吞吐通道应该采用横向放置规划! 控制通路采用纵向放置规划! Altera至此以后,一直沿袭这种结构规划.因此,如果你想有效利用好Altera的产品,就应该遵守这个规则.但是要说明的,真正能体现性能的东西,也许 ..

[查看全文]

单片机多机冗余设计及控制模块的VHDL语言描述

2012-06-02

刘先昆 潘红兵

16

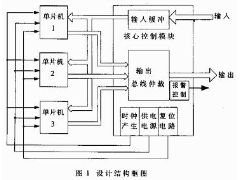

摘要:以三个单片机组成的系统为例介绍一种单片机多机冗余容错设计。阐述设计中关键的时钟同步技术和总线仲裁方法,给出控制模块的VHDL语言描述。 本文提出一种表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复杂的机间通讯协议实现系统重构,不太注重系统的实时性。本方 ..

[查看全文]

SPI串行总线接口的Verilog实现

2012-06-02

孙丰军 余春暄

20

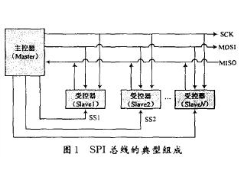

摘 要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。重点描述了SPI串行总线接口在一款 ..

[查看全文]

Xilinx公司FPGA设计技术问答

2012-06-02

9

问:我在ISE4.1中,用fpga express verilog编译的某些文件,用modelsimxe只能前仿,不能后仿,不知5.1i是否有改进? 答: 4.1i支持用Modelsim XE实现行为级仿真和时间仿真,5.1I也同样。请用热线(china_support xilinx.com)打开一个例子并在4.1i/Modelsim XE运行时间仿真以解决你的问题。 问:和5.1结合比较好的验证工具 ..

[查看全文]

Nios II开发常见问题

2012-06-02

12

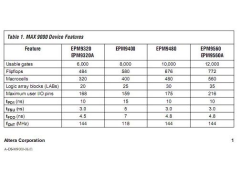

许多朋友在进行Nios II系统的学习,开发中,常常会遇到许多问题;我也会经常接到许多E-Mail,以及电话,询问一些nios开发中的问题。我对这些问题进行了总结,写成了这篇文章。如果本文能对您有一点点帮助,我都会感到非常高兴。 对于许多问题,您仍然需要参考Altera提供的官方参考文档以及随机的help文档。 一。硬件相关: 1.EP ..

[查看全文]

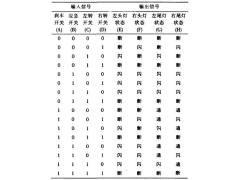

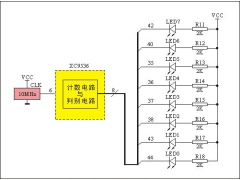

汽车车灯控制系统的VHDL语言实现

2012-06-02

郑应民

11

当前数字电路系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。利用大规模可编程逻辑器件CPLD(Complex Programmable Logic Device)进行ASIC设计,可以直接面向用户需求,根据对系统的功能要求自上而下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成元器件。目前,系统级的仿真工具也已出现.这样可以大 ..

[查看全文]

VHDL 编程的一些心得体会

2012-06-02

8

VHDL 是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。 与另外一门硬件描述语言 Verilog HDL 相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且 VHDL 具有设计重用、大型设计能力、 ..

[查看全文]

fir滤波器的Verilog程序

2012-06-02

38

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date:17:01:38 10/09/06 // Design Name: // Module Name:ppeifir // Project Name: // Target Device: // Tool versions: // Description:用Verilog编写的fir滤波器程 ..

[查看全文]

用Verilog-HDL做CPLD设计(时序逻辑电路的实现)

2012-06-02

常晓明 李媛媛

37

Verilog-HDL与CPLD/FPGA设计应用讲座 第 8 讲 用Verilog-HDL做CPLD设计 时序逻辑电路的实现 8.1 闪烁灯的实现 8.2 流水灯的实现 8.3 可编程单脉冲发生器 在第七讲中,已经介绍了组合逻辑电路的实现。组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。时序逻辑电路则不同于它,其特点是:在任意 ..

[查看全文]

VHDL设计举例:步进电机控制器

2012-06-02

26

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.std_logic_unsigned.ALL; USE IEEE.std_logic_arith.ALL; ENTITY step_motor IS PORT( f, p, d: INSTD_LOGIC:='0'; speed : inSTD_LOGIC_VECTOR(1 downto 0); coil : OUTSTD_LOGIC_VECTOR(3 downto 0) ); END step_motor; ARCHITECTURE behavior OF s ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317