Verilog HDL代码描述对状态机综合的研究

2012-06-02

李玲 王祖强 陈东海

10

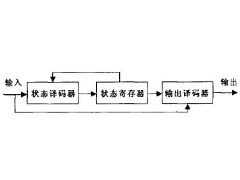

1 引言 Verilog HDL作为当今国际主流的HDL语言,在芯片的前端设计中有着广泛的应用。它的语法丰富,成功地应用于设计的各个阶段:建模、仿真、验证和综合等。可综合是指综合工具能将Verilog HDL代码转换成标准的门级结构网表,因此代码的描述必须符合一定的规则。大部分数字系统都可以分为控制单元和数据单元两个部分,控制单元 ..

[查看全文]

Verilog HDL设计练习进阶(二)

2012-06-02

12

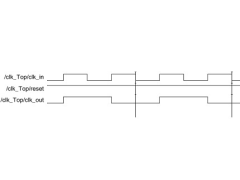

练习二. 简单时序逻辑电路的设计 目的:掌握基本时序逻辑电路的实现。 在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型,我们通常使用always块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个1/2分频器的可综合模型。 // half_clk.v: module half_clk( ..

[查看全文]

基于Nios的DDS高精度信号源实现

2012-06-02

鲜华

18

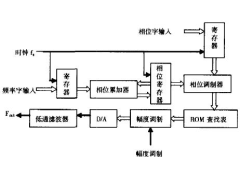

摘要:直接数字频率合成器DDS具有极高的分辨率、频率转换速度快、相位噪声低等优点。以ALTERA公司的CPU软核Nios为基础,利用Quartus II软件和Sopc Builder,采用两级DDS和动态分频法,提高了信号源的精度。采用双口ROM可以很方便的同时输出两路具有一定相位差的信号,而且频率幅度可调。另外着重介绍了怎样用Matlab产 ..

[查看全文]

基于CPLD的交通灯控制系统

2012-06-02

孙芹芝 张瑾 苏晓鹭

22

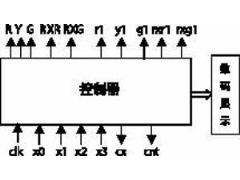

引言 EDA技术是用于电子产品设计中比较先进的技术,可以代替设计者完成电子系统设计中的大部分工作,而且可以直接从程序中修改错误及系统功能而不需要硬件电路的支持,既缩短了研发周期,又大大节约了成本,受到了电子工程师的青睐。 实现路口交通灯系统的控制方法很多,可以用标准逻辑器件、可编程序控制器PLC、单片机等方案 ..

[查看全文]

怎样用modelsim做后仿真

2012-06-02

26

怎样用modelsim做后仿(编译工具采用quatus) step1: 在qurtus改变编译选项: assignments->EDA tool setting:选择verilog还是vhdl。 step2: 编译。你会在你的工程所在目录 看到一个simulation的目录,这里面有你生成的网表文件和标准延时文件。 step3: 在目录:\quartus\eda\sim_lib找到你选用器件对应的库文件,将库文件 ..

[查看全文]

FPGA三国志-第二篇/结构篇

2012-06-02

wisdomz

9

Altera FPGA的速度没有Xilinx的速度快,错!当然这种非对称的结构,你必须有一定的了解,才可以更好的利用.也就是要遵循: 大的数据吞吐通道应该采用横向放置规划! 控制通路采用纵向放置规划! Altera至此以后,一直沿袭这种结构规划.因此,如果你想有效利用好Altera的产品,就应该遵守这个规则.但是要说明的,真正能体现性能的东西,也许 ..

[查看全文]

基于MATLAB的DSP调试方法

2012-06-02

刘瑞华 潘建军

14

MATLAB 具有强大的分析、计算和可视化功能,利用MATLAB 提供的数十个专业工具箱,可以方便、灵活地实现对自动控制、信号处理、通信系统等的算法分析和仿真,是算法设计人员和工程技术人员必不可少的软件工具。 数字信号处理器(DSP)作为一种可编程专用芯片,是数字信号处理理论实用化过程的重要技术工具,在语音处理、图像 ..

[查看全文]

ModelSim SE仿真Altera库的建立

2012-06-02

shemily

28

(注:最近自己准备做后仿真,到坛子里看看了,发现一开始建库就是一个很大的问题。为了便以自己学习也为了给大家省点事,我花了十来个小时整理了一些资料,全部资料来自edacn.net/bbs的ModelSim的〈库〉,在下面的资料中不能一一列出作者,请各位网友多多包涵。下面的资料是大家的成果。by CHY 07.04.05) 1. modelsim怎 ..

[查看全文]

关于NIOS II对FLASH的支持情况

2012-06-02

渐风

17

哥们我也是第一次正儿八经搞NIOS II,很多奇怪的问题都被俺碰上了,从头到尾一共花了将近一个月,终于把NIOS给活生生跑起来了。虽然浪费了很多时间,但经验值了提高了一些。 现在把FLASH的问题写一下给大家分享,希望能对各位有点帮助。 NIOS II的手册说的很明白,只支持具有CFI接口的FLASH器件。用AMD和INTEL的肯定没有 ..

[查看全文]

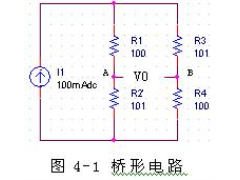

从实例中学习OrCAD-PSpice 10.3-AA(第4章灵敏度分析工具)

2012-06-02

25

想要调用PSpice–AA进行电路优化设计,一般是先进行灵敏度(Sensitivity)分析:以便确定电路中对电路特性影响最大的关键元件参数进行优化。OrCAD9.2以前版本的灵敏度分析,由于有大量数据输出问题没有解决,故只局限于作直流灵敏度分析,置于直流工作点分析内。 直流灵敏度分析:虽然电路特性完全取决于电路中的元器 ..

[查看全文]

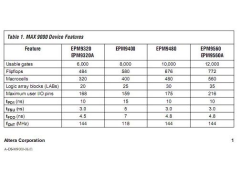

Altera FPGA、CPLD 学习笔记

2012-06-02

11

1.硬件设计基本原则 速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用 & ..

[查看全文]

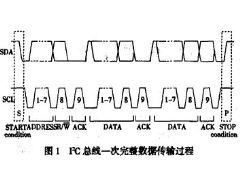

FPGA有限状态机模拟I2C总线设计

2012-06-02

潘小冬

20

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 136

-

C99语法规则2024年11月16日 1177

-

FreeRTOS 动态内存管理2024年11月12日 504

-

一款常用buffer程序2024年11月06日 133

-

1602液晶显示模块的应用2012年08月03日 205

-

GNU C 9条扩展语法2024年11月18日 312

最新文章

-

Corext-M3中断的具体行为2025年11月11日 90

-

优秀的字符串哈希算法-ELFhash2024年11月26日 119

-

SD卡TF卡引脚定义2024年11月26日 128

-

C语言string.h常用函数重点说明2024年11月22日 75

-

C语言下划线命名法2024年11月22日 88

-

C数组 结构体 联合体快速初始化2024年11月22日 65

热门文章

-

C99语法规则2024年11月16日 1177

-

51单片机LED16*16点阵滚动显示2012年09月05日 677

-

FreeRTOS 动态内存管理2024年11月12日 504

-

ARM9远程图像无线监控系统2012年07月03日 440

-

如何实现STM32F407单片机的ADC转换2024年11月15日 318

-

用单片机模拟2272软件解码2012年09月06日 317