介绍状态机的一种书写方式

2013-03-17

11

借用zqadam的逻辑改的: `define S1 0 `define S2 1 `define S3 2 `define S4 3 `define S5 4 `define S6 5 `define S7 6 `define S8 7 module clk_gen2 (clk,reset,clk1,clk2,clk4,fetch,alu_clk); input clk,reset; output clk1,clk2,clk4,fetch,alu_clk; wire clk,reset; reg clk2,clk4,fetch,alu_clk; reg[7:0] state,next_state ..

[查看全文]

消除状态机毛刺策略探讨

2013-03-11

鲁玲 刘大年

14

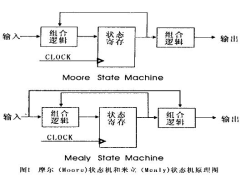

随着EDA技术的高速发展,以大规模和超大规模器件FPGA/CPLD 为载体、以VHDL(硬件描述语言)为工具的电子系统设计越来越广泛。有限状态机(简称状态机)作为数字系统控制单元的重要设计方案之一,无论与基于VHDL语言的其他设计方案相比,还是与可完成相似功能的CPU设计方案相比,在运行速度的高效、执行时间的确定性和高可 ..

[查看全文]

基于RTL综合策略的状态机优化方法

2013-03-10

石松华 任浩琪

20

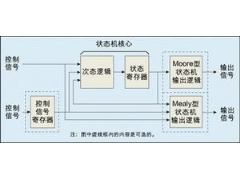

有限状态机及其设计技术是数字系统设计中的重要组成部分,是实现高效率、高可靠性逻辑控制的重要途径。大部分数字系统都可以划分为控制单元和数据单元两个组成部分。通常,控制单元的主体是一个状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。状态机性能的好坏对系统性能有较大的影响。良好的状态机的实 ..

[查看全文]

VHDL设计MOORE型有限状态机时速度问题的探讨

2013-03-10

朱小莉 陈迪平 王镇道

22

1 引言 随着微电子技术的迅速发展,人们对数字系统的需求也在提高。不仅要有完善的功能,而且对速度也提出了很高的要求。对于大部分数字系统,都可以划分为控制单元和数据单元两个组成部分。通常,控制单元的主体是一个有限状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。MOORE型有限状态机的设计方 ..

[查看全文]

用STATECAD快速设计有限状态机

2013-02-08

14

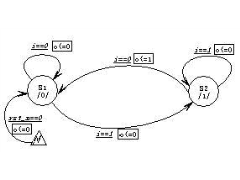

数字系统通常划分为信息处理单元和控制单元。信息单元主要进行信息的传输和运算, 而控制单元的主要任务是控制信息处理单元的微操作的顺序。控制单元的实现方式有: 有限状态机、控制寄存器和微代码控制器等。有限状态机在时间尺度上对其控制信号进行离散化控制, 利用状态转移使控制信号在有限状态机的状态节拍控制下变化, 以实 ..

[查看全文]

FPGA/CPLD状态机的稳定性研究

2012-12-25

宋烈武 石强

17

摘要 在FPGA/CPLD设计中频繁使用的状态机,常出现一些稳定性问题,本文提出了一些解决方法,实验表明该方法有效地提高了综合效率. 随着大规模和超大规模FPGA/CPLD器件的诞生和发展,以HDL(硬件描述语言)为工具、FPGA/CPLD器件为载体的EDA技术的应用越来越广泛.从小型电子系统到大规模SOC(Systemonachip)设计,已经无 ..

[查看全文]

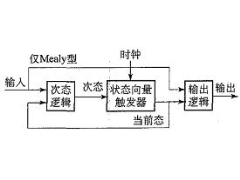

高速环境下的状态机设计策略

2012-11-10

14

通过减少寄存器间的逻辑延时来提高工作频率,或通过流水线设计来优化数据处理时的数据通路来满足高速环境下FPGA或CPLD中的状态机设计要求。本文给出了采用这些技术的高速环境状态机设计的规范及分析方法和优化方法,并给出了相应的示例。 为了使FPGA或CPLD中的状态机设计满足高速环境要求,设计工程师需要认识到以下几点 ..

[查看全文]

让Verilog仿真状态机时可以显示状态名

2012-10-31

RickySu

32

Situation: 我们平时使用Verilog进行状态机编码时,通常使用parameter对状态名进行定义,这样写Case语句的时候就不会对这一串10摸不着头脑。可是通常这样做的话,在Modelsim里看到的还是一串10,使排错非常困难,特别是在用OneHot编码的时候,就看到一串0中间的一个1 #_# 简直要疯掉。 Question: 我们可不可以像VHDL一样 ..

[查看全文]

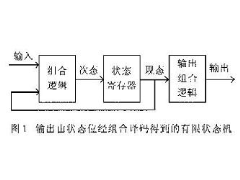

有限状态机的VHDL优化设计

2012-10-29

洪国玺 董辉

15

1.引言 当前以硬件描述语言为工具、逻辑器件为载体的系统设计越来越广泛。在设计中,状态机是最典型、应用最广泛的电路模块,其在运行速度的高效、执行时间的确定性和高可靠性方面都显现出强大的优势。状态机及其设计技术水平决定了系统设计的优劣[1]。如何设计一个最优化的状态机是我们必须面对的问题。 本文将详细讨论状态 ..

[查看全文]

状态机性能考察(代码编写)

2012-10-18

16

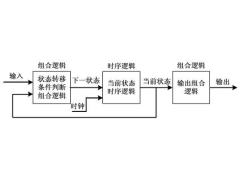

• 状态机代码编写 在大型系统中编码风格会极大的影响状态机的性能。状态机的代码编写方式一般是采用所谓的双always块风格。其一是时序逻辑,在时钟沿到来时将状态向量赋值为下一状态。其二是纯组合逻辑,使用case或if/else语句枚举当前状态和输入可能的组合,并指定下一状态和输出。 但是这并不总是最佳的选择,对于不同的 ..

[查看全文]

基于CPLD的一种容错状态机的设计

2012-10-15

刘华伟 郭创

16

状态机是一种十分重要的时序电路,常用于描述数字系统的控制单元,在数字系统有着广泛的应用,如步进电机、数据存储器的读写、总线控制器等。本文结合具体课题;采用ALTERA的CPLD器件EPM7032实现了一种容错的状态机;采用VHDL语言编程,实际使用效果良好,不仅调试方便,而且增加了系统配置的灵活性,大大缩短了系统开发周期。 ..

[查看全文]

推荐文章

最新文章

热门文章