Verilog阻塞式赋值与非阻塞式赋值的分析

2012-06-02

nsun

19

在Verilog HDL中,有两种过程性赋值方式,即阻塞式(blocking)和非阻塞式(non-blocking)。这两种赋值方式看似差不多,其实在某些情况下却有着根本的区别,如果使用不当,综合出来的结果和你所想得到的结果会相去甚远。 Tip:所谓过程性赋值就是指在initial或always语句内的赋值,它只能对寄存器数 据类型的变量赋值。 阻塞式 ..

[查看全文]

Verilog HDL设计练习进阶(二)

2012-06-02

9

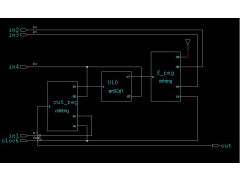

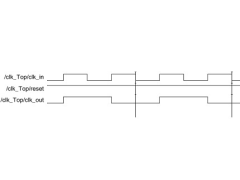

练习二. 简单时序逻辑电路的设计 目的:掌握基本时序逻辑电路的实现。 在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型,我们通常使用always块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个1/2分频器的可综合模型。 // half_clk.v: module half_clk( ..

[查看全文]

Verilog HDL设计练习进阶(九)

2012-06-02

7

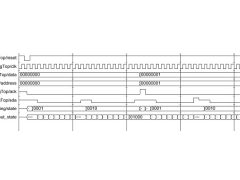

练习九.利用状态机的嵌套实现层次结构化设计 目的:1.运用主状态机与子状态机产生层次化的逻辑设计; 2.在结构化设计中灵活使用任务(task)结构。 在上一节,我们学习了如何使用状态机的实例。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是状态机套用状态机,从而形成树状的控制核心。这一点 ..

[查看全文]

ADC0809 VHDL控制程序

2012-06-02

50

--文件名:ADC0809.vhd --功能:基于VHDL语言,实现对ADC0809简单控制 --说明:ADC0809没有内部时钟,需外接10KHz~1290Hz的时钟信号,这里由FPGA的系 --统时钟(50MHz)经256分频得到clk1(195KHz)作为ADC0809转换工作时钟。 --最后修改日期:2004.3.20 library ieee; use ieee.std_logic_1164.all; use ieee.std ..

[查看全文]

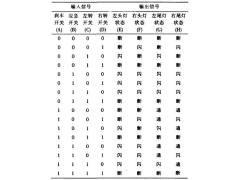

汽车车灯控制系统的VHDL语言实现

2012-06-02

郑应民

9

当前数字电路系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。利用大规模可编程逻辑器件CPLD(Complex Programmable Logic Device)进行ASIC设计,可以直接面向用户需求,根据对系统的功能要求自上而下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成元器件。目前,系统级的仿真工具也已出现.这样可以大 ..

[查看全文]

debussy和modelsim协同仿真(VHDL)

2012-06-02

22

1、 编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。 2、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中 3、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录 4、 ..

[查看全文]

分频器的VHDL描述

2012-06-02

7

在数字电路中,常需要对较高频率的时钟进行分频操作,得到较低频率的时钟信号。我们知道,在硬件电路设计中时钟信号时非常重要的。 下面我们介绍分频器的VHDL描述,在源代码中完成对时钟信号CLK的2分频,4分频,8分频,16分频。 LIBRARYIEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IE ..

[查看全文]

一种用VHDL设计嵌入式Web Server的方案

2012-06-02

13

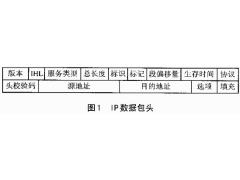

摘要:近几年嵌入式Internet开始迅猛发展,但绝大多数嵌入式Internet都使用微控制器和相应的软件来实现。本文介绍一种基于硬件来实现嵌入式Web Server的方案。该方案的核心思想是用VHDL语言来设计实现,并且用FPGA进行验证。 关键词:VHDL Internet协议 控制信息协议 数据报 最近几年随着Internet应用的迅猛发展,Intern ..

[查看全文]

VHDL 编程的一些心得体会

2012-06-02

6

VHDL 是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。 与另外一门硬件描述语言 Verilog HDL 相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且 VHDL 具有设计重用、大型设计能力、 ..

[查看全文]

Verilog交通灯控制器程序

2012-06-02

6

交通灯控制器 /* 信号定义与说明: CLK: 为同步时钟; EN: 使能信号,为1 的话,则控制器开始工作; LAMPA: 控制A 方向四盏灯的亮灭;其中,LAMPA0~LAMPA3,分别控制A 方向的 左拐灯、绿灯、黄灯和红灯; LAMPB: 控制B 方向四盏灯的亮灭;其中,LAMPB0 ~ LAMPB3,分别控制B 方向的 左拐灯、绿灯、黄灯和红灯; ACOU ..

[查看全文]

单片机多机冗余设计及控制模块的VHDL语言描述

2012-06-02

刘先昆 潘红兵

13

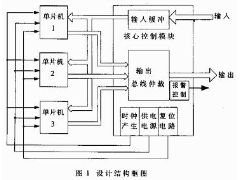

摘要:以三个单片机组成的系统为例介绍一种单片机多机冗余容错设计。阐述设计中关键的时钟同步技术和总线仲裁方法,给出控制模块的VHDL语言描述。 本文提出一种表决式单片机多机冗余设计方案。该方案不同于中央系统的多机冗余设计。大规模系统冗余大多采用完善而复杂的机间通讯协议实现系统重构,不太注重系统的实时性。本方 ..

[查看全文]

SystemVerilog语言简介

2012-06-02

40

SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、 接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。SystemVerilog由Accellera开发,它主要定位在芯片的 ..

[查看全文]

推荐文章

最新文章

热门文章