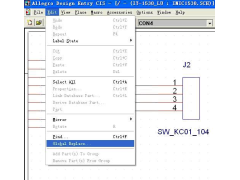

allegro加载skill函数到菜单

2013-01-12

Sutong

17

学习了一段时间allegro,你是不是也对SKILL函数有了一定的认识,也收集了不少skill函数吧,但是不是又对函数的应用感到麻烦和被动。现在就说一下怎样把函数加载到应用菜单,利用鼠标点击轻松执行。因为好多人不知道怎么使用,我也是摸索出来的,供大家参考,独乐乐,与人乐乐,孰乐?! 1、 设定环境变量 : 首先建立SKILL和SU ..

[查看全文]

Allegro约束管理器(Back-End)

2013-01-07

18

一、 约束管理器(BACK-END) 在HDL的相应课程中约束是表格代替PCB中的Constraints设置让人容易理解,这里用SigXplorer图形化可以更深刻的理解约束的定义和为什么。 (一)、规划网络(根据Cadence教程) 1、简单规划: 选取要操作的网络显示:Display/Blank Rats/All隐藏所有的网络,打开约束管理器,Display/Show Rats/Net切 ..

[查看全文]

在Allegro 中如何输入原理图的网表(Netlist)文件?

2013-01-05

17

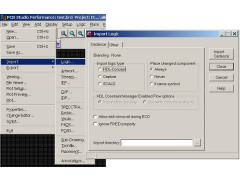

在Allegro 中执行File→Import→Logic…命令,得到输入逻辑(Import Logic)对话框。 在输入逻辑(Import Logic)对话框的Cadence 表格中选择相应的原理图输入类型(Import logic type)。例如,HDL-Concept、Capture (包括Capture CIS)或SCALD。 当你选择输入逻辑类型(Import logic type)为HDL-Concept 时, ..

[查看全文]

orcad中快速將所有零件的Footprint加上

2013-01-03

23

方法一 : 一页一页修改,打开某页,按CTRL+F->part->*,选中当前页所有器件,再点右键,选属性,在弹出对话框中按要修改REF 排序,用左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填入封装就成批修改了 方法二 : 先进入Project Manager,选择顶层原理图,选Edit-Browse Parts,用点击和Shift+点击选择所有元 ..

[查看全文]

Cadence psd15.1使用笔记

2012-12-28

52

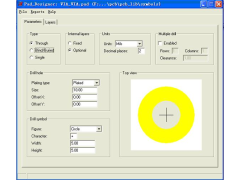

Cadence psd15.1是一个很强的PCB板图制作工具,我根据这段时间我使用psd15.1的过程,总结了使用的具体的流程以及比较重要的注意点。 在psd中,强调先确定器件的物理封装,然后再画原理图封装,然后绘制原理图,最后绘制PCB图。这是很重要的一点,贯穿整个设计过程。当然也可以先建立原理图封装,然后将原理图封装和物理封 ..

[查看全文]

ORCAD中一次性修改元件属性

2012-12-25

leal_huang@yahoo.cn

23

在电路的绘制过程中有时需要修改元件的属性,现在介绍如何应用一次性修改方法进行修改,应用该方法可以大大提高我们的工作效力,这是我工作中总结的,现同大家分享. 我以例举一次性修改元件封装为例子. Step1:打开原理图,在管理窗口中选中原理图文件,如下 Step2: 执行Edit/Browse/Parts Step3: 直接点OK Step4: 现在出现元件浏 ..

[查看全文]

如何在Allegro环境下运行SKILL

2012-12-23

24

1、如何在PCB Editor 环境下启动SKILL 命令行解释器界面? 直接输入settelskill,然后你就会看到一个新的界面,这个界面就是用来运行SKILL 函数和命令的解释器。 当然,如果你不觉得界面太小,可以直接在命令行中输入skill ,然后运行SKILL函数和命令,也可以正常执行,退出可以直接输入exit。 2、如何执行写在文件中的SKILL 函 ..

[查看全文]

Allegro使用简介

2012-12-23

姚澜

76

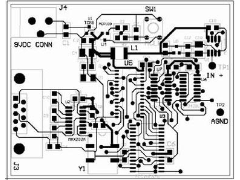

一.零件建立 在Allegro 中, Symbol 有五种, 它们分别是Package Symbol 、Mechanical Symbol、Format Symbol、Shape Symbol、Flash Symbol。每种Symbol 均有一个Symbol Drawing File(符号绘图文件), 后缀名均为*.dra。此绘图文件只供编辑用, 不能给Allegro 数据库调用。Allegro 能调用的Symbol 如下: Package Symbol 一般元 ..

[查看全文]

ALLEGRO 约束规则设置步骤

2012-12-19

tzyhust@163.com

44

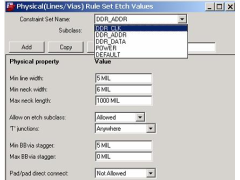

本文是我对约束规则设置方面的一些理解,希望对新手能有所帮助。由于本人水平有限,错误之处难免,希望大家不吝赐教! 在进行高速布线时,一般都需要进行线长匹配,这时我们就需要设置好 constraint 规则,并将这些规则分配到各类 net group 上。下面以 ddr为例,具体说明这些约束设置的具体步骤。 1. 布线要求 DDR 时钟:线宽 ..

[查看全文]

cadence 如何出具有盲埋孔的drill

2012-12-18

15

旧板适用 1 首先在MANUFACTURING Class 增加需要的钻孔图层(subclass);例如1-4-1的基板叠构需要(L1-L2),(L2-L5),(L5-L6)等三张钻孔图. 1.1 选择Setup>Subclass 指令. 1.2 在出现的Define Subclass 对话框内,选择MANUFACTURING 左边的按钮. 1.3 接著出现Define Non-conductor Subclass 对话框.在New Subclass 右边 ..

[查看全文]

使用Allegro SI分析串扰

2012-12-05

86

1 概要 高速电路板在进行信号完整性分析的时候,和反射一起的串扰噪声的影响也必须考虑。 本文将介绍串扰噪声的理论基础及如何使用Allegro PCB SI对串扰进行分析: 2 所谓串扰噪声 ※ Aggressor・・・入侵网络 ※ Victim・・・受害网络 众所周知,信号传输线路周围有电磁场发生。当 ..

[查看全文]

Allegro铺铜的学习

2012-12-05

无名小卒

186

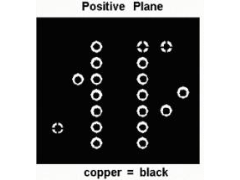

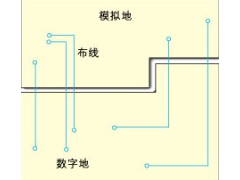

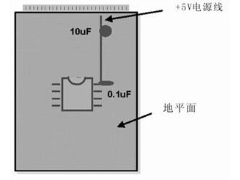

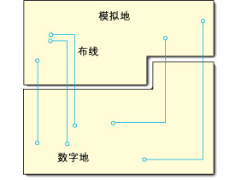

说到电源,真是头疼,设计2410板子的PCB之初不知道电源应该怎么设,所有也就放下了,后来在看书的过程中也接触到了铺铜,但是没有细看,结果是用时才知道很重要,为了加深理解,需要写下这篇学习的过程。 首先要理解什么是正片和负片 ,结合网上的资料来理解一下: 正片实际就是能在底片上能看到的就是存在的 负片实际上就是在 ..

[查看全文]

推荐文章

-

怎样设计一块好的PCB板2012年07月28日 60

-

高速PCB设计指南(三)2013年03月27日 155

-

PCB布线设计(二)2013年03月23日 45

-

混合信号PCB的分区设计2013年03月04日 31

-

高速PCB设计指南(六)2012年12月29日 32

-

PCB布线设计(一)2012年10月22日 13

最新文章

-

常用贴片电阻尺寸功率对照表2024年11月22日 51

-

常用电阻,电容,电感标称值2024年11月22日 94

-

PSPICE 的应用2013年04月06日 38

-

Protel DXP的电路仿真设计2013年04月04日 22

-

Gerber转protel的方法2013年04月04日 32

-

在PADS中添加表面型测试点2013年04月03日 57

热门文章

-

PROTEL 99SE的打印设置2013年02月08日 385

-

Protel dxp等长走线2013年01月02日 333

-

Cadence 中添加工艺库文件步骤2013年01月16日 292

-

电气安全距离要求及分类2012年09月06日 276

-

Allegro铺铜的学习2012年12月05日 186

-

在ORCAD中整体修改网络名称2012年07月26日 177