MC68HC08的锁相环编程指导

锁相环是什么?是一种倍频器,它将时钟基频(CGMXCLK)进行分频,产生PLL倍频信号(CGMVCLK),然而,由于它基础理论抽象,很难懂。本文以尽量简明的原则,帮大家学好锁相环初始值的设定

寄存器:

PCTL:锁相环控制寄存器 所在地址 $036

通过PRE预分频值查此表可计算出第三位,第二位值以及PRE值

|

PRE1 |

PRE2 |

PRE值 |

预分频系数 |

|

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

2 |

|

1 |

0 |

2 |

4 |

|

1 |

1 |

3 |

8 |

通过VCD电源系数查此表可计算出第一位,第零位以及VPR系数

|

VPR1 |

VPR0 |

VPR值 |

VCD电源系数 |

|

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

2 |

|

1 |

0 |

2 |

4 |

|

1 |

1 |

3 |

8 |

其中PRE和VCD由fbus(内部时钟速率)确定,输出时钟为4*fbus,确定方式见下表

|

Fbus |

PMSH值 |

PMSL值 |

PMRS值 |

PRE值 |

VPR值 |

|

2 |

0 |

F5 |

D1 |

0 |

0 |

|

2.4576 |

1 |

2c |

80 |

0 |

1 |

|

2.5 |

1 |

32 |

83 |

0 |

1 |

|

4.0 |

1 |

E9 |

D1 |

0 |

1 |

|

4.9152 |

2 |

58 |

80 |

0 |

2 |

|

5.0 |

2 |

63 |

82 |

0 |

2 |

|

7.3728 |

3 |

84 |

C0 |

0 |

2 |

|

8.0 |

3 |

D1 |

D0 |

0 |

2 |

典型应用:

PCTL=0x00;//禁止PLL

PCTL=0x22;//00100010,开启PLL,选择PRE=0,VPR=1

PCTL_PLLON=1;//使能PLL

PCTL_BCS=1;//输出时钟分频选择

PBWC:PLL控制寄存器 所在地址 $037

|

地址 |

7 |

6 |

5 |

|

|

AUTO 带宽控制方式 |

LOCK 带宽是否已稳定(只读) |

|||

|

置1 |

自动 |

锁定 |

||

|

置0 |

手动 |

不锁定 |

||

|

默认 |

0 |

0 |

还有几个寄存器,一般保持复位的值不变,知道即可

PMSH,PMSL:PLL倍率选择器 所在地址$038,$039

PMSH低四位有效,PMSL全部有效。复位后都为0

PMRS:电源范围系数 复位后为0

PMDS:PLL基时钟分频选择器 所在地址$3B

锁相环设置七步走:

(1) 禁止PLL:PCTL=0;

(2) 选择自动控制方式 PBWC=0x80;

(3) 设置分频系至PMSH和PMSL

(4) 设置输出范围系数至PMRS

(5) 根据典型参数表设置PCTL,其中包括PRE值(由Vpr1,Vpr0联合确定),VPR值(由PRE1,PRE0联合确定)和

锁相环使能PCTL_PLLON=1,等待稳定,稳定后,设PBWC_LOCK=0;

(6) 设置输出时钟为CGMVCLK的二分频PCTL_BCS=1

实例:

PCTL=0x00;//step1

PBWC=0x80;//step2

PMSH=0x02;//step3

PMSL=0x58;

PMRS=0x80; //step4

PCTL=0x22; //step5

PCTL_PLLON=1; //step6

PBWC_LOCK=0;

PCTL_BCS=1; //step7

注意锁相环要经过两次使能,如上所示PCTL=0x22; (第一次) PCTL_PLLON=1;(第二次)

其实作为初学,可以直接把典型的代码复制过来,如果想DIY的话,就通过“常用PLL系数表”进行设置即可。

-

一款高温报警电路2024年11月13日 81

-

可燃气体全自动点火器2012年09月22日 76

-

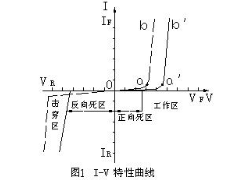

LED参数与特性2012年09月18日 118

-

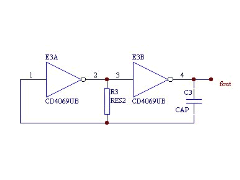

RC振荡电路的几种接法2012年09月10日 221

-

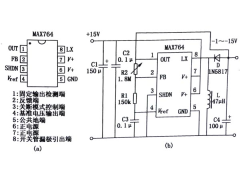

MAX764极性反转电路2012年08月24日 47

-

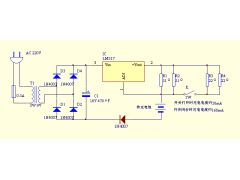

实用恒流充电器2012年08月18日 175

-

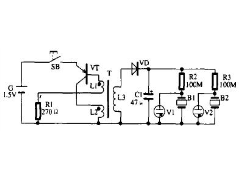

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4875

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

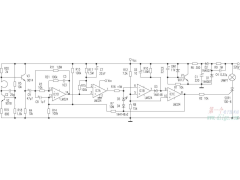

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499