三 . 用Checkplus 工具,对原理图进行检查。

回到Project Manager 窗口,选择Tools --- Checkplus.如下图:

选择其中不同项,可对原理图进行相应检查,如上图即可检查单节点等。当发生错误时,再回到Concept-HDL 环境,使用Tools---Markers 对错误进行定位并改之。

四.层次化设计:

随着电路设计逐渐趋于模块化以及设计复杂性的提高,层次化设计越来越多地被采用。层次化设计就是采用模块的方法,将一个设计嵌入到另一个设计中。这样设计出的原理图层次清晰,而且由模块描述的电路,更容易被复制和重新利用。

它的文件目录结构如下:

进行层次化设计需注意以下事项:

1..sch 和.sym 文件名必须相同。如:module1.sch 和module1.sym

2..sch 图中的I/O 信号名必须和相应的.sym 图中的管脚名相同。

3.I/O 信号必须具有如下端口符号:

- Inport

- Outport

- Ioport

▲▲注意:上述三个端口符号与出入页信号OFFPAGE 是两种不同的符号。

4.在层次化设计中,有三种不同的信号类型:

Local:局域信号在一个模块设计中是唯一的。不同模块中的相同信号名并不相连。

Global:全局信号用于不同模块中的相同功能管脚(如:电源,地)之间的连接。通常表示为:信号名G。

Interface:I/O 信号,用于告诉其他模块(或设计),这些信号通过端口符号连接在原理图中。

5.为区别原理图器件符号和模块符号,模块符号统一使用下图所示式样:

通过一个简单实例介绍产生层次化设计的两种方法:

例如:

1. TOP-DOWN 方法

A.产生顶层原理图TOP.SCH.1.1:

a. 在top.sch.1.1 原理图中使用Block---add 添加代表模块的符号block1,

用Block----rename 命令将其改名为module1

用Block----strecth 改变其大小,如下图:

b. 用Block----add pin 给其添加pin

其中:

Input pin:A , EN

Output pin: B

如下图:

c.完成该页原理图后,选择File---save

B.产生模块module1 的原理图:

a.File ---- Open

点击Open,进入module1.sch.1.1 编辑环境,如下图:

b.绘制module1 的原理图:

▲ 注意:module1.sch 图中的信号名必须和相应的module1 中的管脚名相同。

c.选择File----save

此时即通过TOP—DOWN 方法完成一个层次化设计。

当你重新打开顶层原理图(即top.sch.1.1),双击module1 模块即会进入下一层原理图。(即:module1.sch.1.1)。

2. DOWN-TOP 方法

A.生成底层设计,如上图(MODULE1.SCH.1.1)

B.生成模块符号。

在Concept-HDL 环境中选择Tools---Generate View,并点击Generate 即产生module1 的模块符号,如下:

C. 在顶层原理图中,调入module1 模块符号,如下图:

D.完成顶层原理图后,存盘。

此时即用DOWN—TOP 方法完成一个层次化设计,也可通过双击顶层模块进入下层设计。

五.用Packager-XL 生成网表文件。

Packager-XL 的输出文件示意图如下:

Pstback.dat:反标注文件。

Pxl.log:报告文件。

Pstchip.dat:原理图中元件的物理封装说明。

Pstxprt.dat:逻辑元件与其物理元件之间对应关系的文件。

Pstxnet.dat:网表文件。

Pxl.state:状态文件。

Pxl.mkr:错误定位文件。

在Concept-HDL 环境下,点击File---Export Physical。或Project Manager 环境中按DESIGN SYNC 按钮。并选择Export Physical.如下图:

若package 成功,将生成网表文件。否则,修改错误直至打包成功。

六.Back Annotate ---- 反标注

在packager 完成后和pcb 板完成后,一般要对电路原理图进行反标注,以使pcb 与原理图保持一致。经过反标后,软件会自动给每个元器件赋予一个序号。如$location=d1…,无需手工给元器件加序号。

七.Packager Utilities

1. Tools --- Packager Utilities --- Bill Of Material 生成料单.

2. Tools --- Packager Utilities --- Netlist Report 可查看网表。

-

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

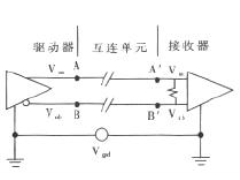

差分信号线的分析和LAYOUT2012年09月16日 144