二.原理图的设计

点击Design Entry 进入 Concept-HDL

Concept-HDL 是Cadence 的电路原理图设计输入环境,下图为Concept-HDL 的目录结构:

在concept 中电路原理图的设计流程如下:

下面就流程的各个部分做简单介绍。

◎1. Adding parts

使用Component---add 命令在原理图中加元器件。

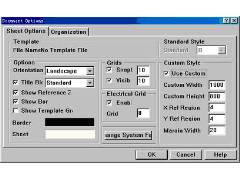

▲注意:为避免调出的元器件连线错位。栅格设置: 栅格为50mil 栅格显示为100mil

首先应放入公司的标准图框(libcdmaFrameA1---A4,A4plus),再在图框内添加所需器件。

其中介绍两个命令:

▲ Version ---- 改变元器件符号版本

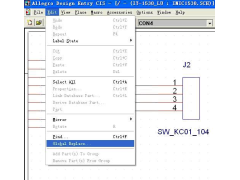

▲ Section ---- 指定逻辑元器件在物理封装中的位置。并显示pin_number.

如下图:

▲ Replace ------ 元件替换。指用一个元件替换图中的另一个元件。

由于涉及到出料单的问题。放置器件(尤其是分立元件)时请按照《CDMA 硬件部原理图设计规范》去做。对含有PPT 信息的器件(PPT 表包含有器件的材料代码和封装信息),可以按下图,选择以Physical 方式从PPT 中调入器件。

◎2. Adding wires

a.使用Wire ---- Draw 命令可在连线的同时,对该线网加信号名。

▲ 靠近需要连线的元件管脚处,使用shift + right 键可以准确快捷地捕捉pin 脚并连线。

b.使用Wire ---- Route 命令可自动完成点到点连线。

◎3. Naming wires

Concept—HDL 可以通过相同信号名自动建立两个线网的连接关系。

使用Wire ---- signame 命令可标记一根线网

使用Text ---- change 命令改正和重新命名信号名。

a.总线

总线的信号名格式为〈msb..lsb>,msb 指总线的最高位。Lsb 指总线的最低位。

当为某根线网定义了总线格式的信号名后,该线将自动加粗,有别于单根信号线。

▲ Bus tap:给拆分出的总线各信号线编号,以便定义每条信号线的连接关系。

b. 逻辑低

在concept—HDL 中,信号名加后缀---"*"表示逻辑低信号。

◎4.添加属性(Property,attribute)

指给元件和信号线添加各种属性。下面仅介绍几个通常给元件添加的属性。

a. LOCATION:定义逻辑元件的物理封装编号。如d1,r5,l3…

b. JEDEC_TYPE:定义了一个逻辑元件的物理封装。原理图中如无此定义或pack_type

定义,则采用元件的缺省封装。

c. POWER_GROUP:定义元件的可替换电源。如:power_group=vddh=vcc3.3v

d. PNUMBER:添入Step2000 内的材料代码。如:PNUMBER=材料代码值

▲ Display ---- Attachments : 显示属性依附关系。

▲ Text ---- Reattach : 属性的重新连接。可通过此命令给属性重新指定附属实体。

◎5. 其它便捷作图命令

▲ Group ---- 组操作。用好group 命令可以提高画图效率。

a. 在原理图中框出要定义为一个组的所有元素。

b. 使用Group ---- Copy All(Copy)或Move 命令对该组进行操作。需要注意的是Copy All 命令可将元件,连线以及连线属性全部复制,而Copy 无法复制连线属性。

◆如果你想跨页拷贝,可新建一个窗口,重复a,b 两个步骤,将要复制的组拷入新建窗口内。

◆ 为使图纸清晰,干净。有时需隐藏一些属性。如:path,可使用Goup--Create--ByExpression 并输入path,再选择Group—Property Display—Invisible 即可。

▲ Global Find ---- 查找命令。你可以通过某个元器件序号或某个网络名在复杂的原理图中将之迅速定位。如下图查找D10.

或选择Net 框,通过网络名,即可快速定位该网络。如下图:

◎6. 存盘

完成原理图的绘制后,将原理图存盘。

-

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

差分信号线的分析和LAYOUT2012年09月16日 144