22 powerpcb 的使用

各位,在使用从网络站点上下来的POWERPCB5.0的时候有在XP环境下有没有出现死掉的情况呢?

怎么解决,或者怎么设置保存时间,或者做一段就存起来呢?

XiaoQY

有自动备份的设置!

在INTERVAL后面改成你所需的间隔时间!

如下图需5分钟!就改为5!

下面的3是所备份的文档数!

23过孔与地和电源相连接

过孔与地和电源想连接是不是都是带差的符号

XiaoQY

你如果设置了花孔的话就会以花孔显示的!

Zxfeng

可以关掉,但为什么要这样呢?

setup--preferences--thermals--show general plane indicate

24 请问各位,对于 SMD 元件,怎么样引出过孔

突然之间发现过孔的引出也是很有讲究的,这样才能方便走线,各位谈谈这方面的经验,比如 SDRAM FLASH 还有BGA的引出!

他们的引出方法是不是也必须一样呢?也就是说各管脚的过孔都是一样的!

布兜

为了看起来整齐,过孔应打在一排。但有时过孔太密会破环平面层,可根据线密度打成几排。比喻1、3、5......pin 一排,2、4、6......pin 一排。但这不是绝对的,因为你要利用过孔改变走线的位置,布线过程中你会体会到的

你要利用过孔改变走线的位置

这句话是什么意思?

布兜

比喻两条连线,要是直接连线是交叉的,你就要通过改变过孔的位置改变走线位置使其平行与另外一端连接。这种问题都是在实际布板过程中体验出的,别人说你可能不理解,遇到了你就会明白。

Dzkcool

也就是说可以调线的顺序

25:在 POWERPCB 中怎么给每个焊盘加上过孔

在POWERPCB中怎么给每个焊盘加上过孔,从焊盘到过孔的距离10MIL是不是有点短呀!

布兜

10mils岂不是焊盘和过孔连在一起了?一般说来BGA过孔到焊盘在100mils以内,但也不要离焊盘太近。

kgx

你加过孔的目的是什么?一般在布线时可以按CTRL加鼠标左键加过孔呀(不过要将END VIA MODE 设置为END VIA)

一个方法是在布线时可以按F4换层,软件自动打过孔,用户可以继续在另一层走线。

一般来说,BGA封装元件的扇出(FANOUT)工作是比较难的。

如果是插装的BGA在元件脚加过孔是没必要的。只需合理分布扇出线就可以布好线。

如果是贴片的话就只能加过孔来分散引出线,但是每个元件脚(外围脚除外)通过过孔后也就当作上面的插装BGA一样布线了,只是贴元件面没有多少走线空间了

26:突然想问大家走线的安排

大家是先走电源和地,然后在走重要的地址线数据线I/O线呢.还是先走I/0然后再走电源和地. 我感觉最好前者先走!

Kgx

先计划好电源和地线的走法,然后将重要的信号线走好,再走其他线

hvll

走线肯定是先走关键信号线、地址线,但同时也得考虑到电源线地线的走势。不过走线时应该都是同步进行的。

Jsckliu

也就是说在走线的时间还是先走信号线再走电源和地线了。

27 在高速电路中,走线和焊盘的连接有没有什么讲究

Kaiko

有,最好是用泪滴焊盘

BILLWANG

同意楼上的观点,最好线宽不要突变。

28 BGA 连线

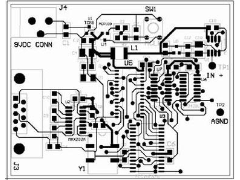

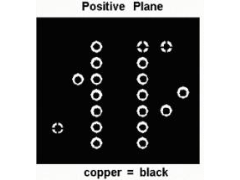

要是在焊盘堆里打孔,那就是打在4个焊盘的中间位置了。将BGA中心以十字划分,分别向左上、左下、右上、右下打孔。

这句话是什么意思,到底是以每个焊盘为中心分别向左上,左下,右上右下打焊盘呢,(至少我看我的参考样板图是这样一来的)

还是在BGA已有的四个焊盘中加过孔

BGA向外出线的时候怎么控制焊盘外边到过孔边的距离是10MIL,我觉的最好还是按照标准来做,这样的话,就可以保证每个焊盘都能外连

布兜

就是说以BGA 芯片中心点为中心,呈放射型像四周打孔。当然也不完全绝对,可根据具体情况灵活对待。

向外引线时,焊盘到过孔10mils?,你从哪里看到的,这咋可能实现呢。

29 BGA 的处理

各位在做BGA的布线的时候,我想先把BGA的连线先连接出来,然后在让他和其他的元器件响亮,不知道这样一来可不可以,请指教

Kgx

当然可以,而且一般也是将连线布出来再布其他地方的。

30:在多层板的处理中对于过孔大家怎么看,在线上打了过孔主要产生些什么影响

布兜

阻抗不连续,引起反射。

还带来时延

wlinda

尽量少打孔,少走弯路

eric57

最重要是線不跨切割

lengcool

走DIASY ROUTE,是走最短的路,有必要再打孔

31 BGA 如何往外拉线?请大家指点

我现在在从BGA往外拉线,但是始终不的要领.自己拉线吧,不知道这BGA走线的规律,和怎么往外拉.没有足够的信心.

按照参考板外外拉吧,因为现在外围的元气件变了很多,会出现很多的过孔

,所以我想各位能不能发给我一些这方面的资料.或者切实指导一下.

从我现在看到的资料来看.BGA焊盘是划片的,并且现在也发现一个问题,每一片的焊盘走的方向也是有方向的.还有这种向外的走线怎么编排,是尽可能先保证走出来呢,还是走线尽可能的减少VIA

Lengcool

先保证BGA的线走出来,等优化时再看打的孔是否多余

32各位,请问怎么把元器件放在珊格上面!

还希望给出确切的步骤!

Kgx

为什么一定要放置到栅格上?你可以将栅格是GRID的倍数即可方便移动。

如:栅格是10mm,GRID是1mm。

33:大家在布线的时候打开 DRC 吗?

XiaoQY

呵呵~~~~~~走习惯了~~~

只要按格点去走就好了~!

不过最好是打开DRC!

Lengcool

其实走在格点上,一般不用打开DRC,布线完成后再检查

34 好多连接电源和地的飞线这是为什么?

各位我的BGA电源和地直接打过孔和电源和地平面连接了,为什么他和别的电源和地还有飞线连接呀, 好象我刚处理完BGA的电源和地的时候这个问题不是太明显,但是保存后为什么再次打开的时候,好象有很多飞线!

Kgx

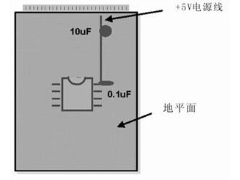

如果同一层有多个电源或地一般还是用分割比较方便,只要给每个网络做一个铺铜框然后灌水即可。

还问个问题在这中分割的电源层中间可不可以走信号线,怎么走呢?

XiaoQY

中间层走线得看你是采用什么方式的输出罗!

cam plane和split/mixe都可用来设为地或电源层,camplane是负片,里面不能走线,但split/mixe是正片,里面可以有走线,可以灌铜。

35 verify design of clearance 错误的解决方法

想问一下,怎么利用验证窗口提示的错误信息,来定位错误,同时修改呢,好象书上面说的

选择DISABLE PANNING 处于没有选择状态,LOCATION定位错误,好象没有任何明亮的标志标识错误!请问班主怎么办!

布兜

在setup/display colors/errors设置颜色,规则检查后会有标记的。

36 还有想问如何在结束的时候铺铜

布兜

在setup/display colors打开要灌铜的层。

鼠标右键select shapes,点击灌铜边框,在工具栏里点击flood图标即可。

你需要先分割电源、地、灌铜(注意,灌铜前应先做好备份,因为有错误修改时,删掉铜是件很浪费时间的事情

这里面的分隔电源和地分别指的是什么?

布兜

分割电源,也就是你在同一电源层上有几个不同的电源,如5V,3V,需要把他们分成5V,3V两部分。用工具栏里的plane area画出两个电源的边框,然后再用flood灌铜。

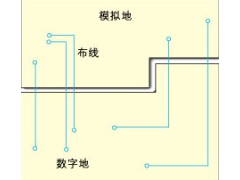

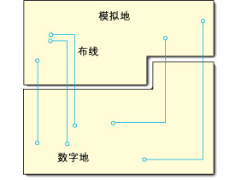

如果地有数字地和模拟地就也需要分割,分割方法同上。

37:请问各位 DRC 检查出现下面的错误是什么问题

LOCATION

latim rule not checked

explanation :

latium rule not checked :component c215 component rule

请问这是什么造成的,怎么样来处理这样的错误!

yuan.lihua

现在可以确认和C215的元气件封装有一定的关系 ,当封装发生变化时候,就会出现上面的错误!

38:背面的元器件文字怎么摆放才符合要求

不会游泳的鱼

你把器件放在bottom层,丝印字符自然就是反的了啊。

单独mirror的话,选中字符,按鼠标右键,有mirror一项的

benbenzhuyi

如果是器件本身的Ref. Des.,那就都是自动的,不用管它;如果自己想放一些表注,一定要镜像,否则将来出来时就是反的!ADD FREE Text的时候,有一项是选择Layer的,还有个Mirror选项。

Lengcool

赞同楼上的说法。

如果是器件本身的Ref. Des.,那就都是自动的,不用管它;如果自己想放一些表注,一定要镜像,否则将来出来时就是反的!ADD FREE Text的时候,有一项是选择Layer的,还有个Mirror选项。

-

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

差分信号线的分析和LAYOUT2012年09月16日 144