3 编写Testbench的一些高级技巧

Verilog HDL提供很多方便和高效的建模语句,这在大多数参考书上都有介绍,在这节,只介绍一些参考教材很少介绍而较有用的建模语句。

1) force 和 release

望文生义,force即是可以对变量和信号强制性地赋予确定的值,而release就是解除force的作用,恢复为驱动源的值。例如:

wire a ;

assign a = 1'b0 ;

initial

begin

#10 ;

force a = 1'b1 ;

#10

release a ;

end

在10 ns时,a 的值由0变为1,在20ns时,a 的值又恢复为0 。

force 和release并不常用,有时,可以利用它们和仿真工具做简单的交互操作。例如,Verilog-XL的图形界面可以方便的将一个信号或变量force为0或1,在 testbench 里,可以检测变量是否被force为固定的值,当被force为固定的值时就执行预定的操作,实现了简单交互操作。

2) 事件

事件有些类似于任务。首先需要定义一个事件,而事件可以作为敏感变量激活一个语句块的操作,事件可由“->”符号进行触发,如下例:

event e1 ; /*定义一个事件*/

always @( e1 ) /*事件e1 作为敏感变量*/

begin

.....

end

initial

begin

—> e1 ; /*创建事件e1来触发上面的always语句*/

.....

end

事件(event )与任务(task)的区别是:执行事件触发后可以立即继续往下执行语句,只起一个触发作用,至于被触发的事件何时执行完毕并不影响程序继续执行。而调用一个任务后,必须等待任务完成才能返回控制权。

3) 模块参数

当一个模块引用另外一个模块时,高层模块可以改变低层模块用parameter定义的参数值,改变低层模块的参数值可采用以下两种方式:

1)defparam 重定义参数

语法:defparam path_name = value ;

低层模块的参数可以通过层次路径名重新定义,如下例:

module top ( .....)

input....;

output....;

defparam U1 . Para1 = 10 ; /*修改实例 U1 模块中的para1 */

M1 U1 (..........);

endmodule

module M1(....);

parameter para1 = 5 ;

input...;

output...;

......

endmodule

在上例中,模块M1参数 para1 的缺省值为5,而模块top实例了M1后将参数的值改为10。

2) 实例化时传递参数

在这种方法中,实例化时把参数传递进去,如下例所示:

module top ( .....)

input....;

output....;

M1 #( 10 ) U1 (..........);

endmodule

在该例中,用#( 10 )修改了上例中的参数para1,当有多个参数时,用逗号隔开,如#( 10 , 5 ,

3 )传递了3个参数值。

模块参数的方法使得模块的重用性更强,当需要在同一个设计中多次实例化同样的模块,只是参数值不同时,就可以采用模块参数的方式,而不必只因为参数不同产生了多个文件。

4) 其他要注意的几个点

4) 注意@与wait的区别

@都是使用沿触发。

wait语句都是使用电平触发。

5) 注意$sreadmemb(h)与$readmemb(h)的区别

$sreadmemb(Memory, StartAddr, FinishAddr, String , ……) :读字符串到Memory。

$readmemb("File", Memory [, StartAddr, [FinishAddr]]) :读取的第一个数字存储在地址

StartAddr,直到FinishAddr。

6) 常用系统任务

$time 返回64位整型时间 。

$stime 返回32位整型时间 。

$realtime 向调用它的模块返回实型模拟时间。

-

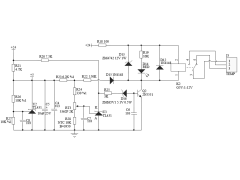

一款高温报警电路2024年11月13日 81

-

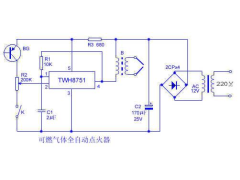

可燃气体全自动点火器2012年09月22日 76

-

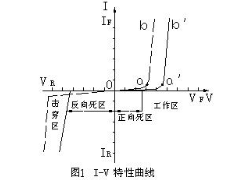

LED参数与特性2012年09月18日 118

-

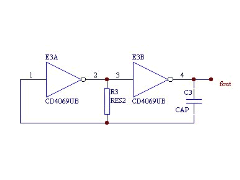

RC振荡电路的几种接法2012年09月10日 221

-

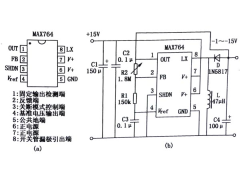

MAX764极性反转电路2012年08月24日 47

-

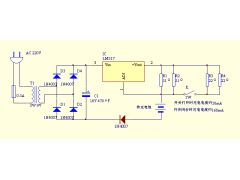

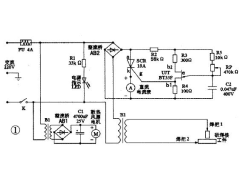

实用恒流充电器2012年08月18日 175

-

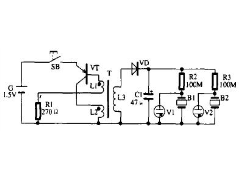

电子催眠器制作2012年08月15日 72

-

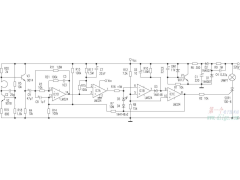

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4875

-

自制微型交流电焊机2012年07月14日 1143

-

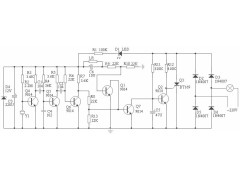

声光控延时开关的制作2024年07月06日 915

-

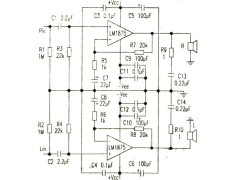

用LM1875替找TDA20302012年09月15日 777

-

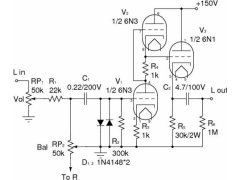

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499