1 Testbench的结构

1) 单顶层结构

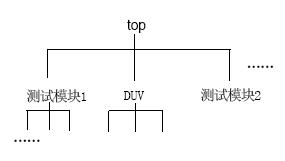

一种结构是testbench 只有一个顶层,顶层再把所有的模块实例化进去。打个比方,类似树结构,只有一个模块有子节点而没有父节点,其它模块都有父节点。如下图结构所示:

测试模块是一些接口模型,接口模型还可能包含了一些激励在内。测试模块和DUV之间通过端口映射进行互连。

2) 多顶层结构

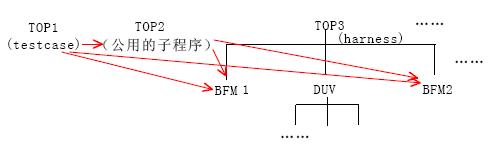

另外一种结构是多顶层结构,如下图所示:

在这种结构中,有一个顶层是作为测试向量模块,一个或多个顶层是一些公用子程序,这些子程序由于完成一些通用的功能被封装成任务、函数等被公用。

还有一个叫harness的顶层,该顶层由DUV和一些接口模型构成一个狭义上的测试平台,其它模块可以调用BFM里面的 task 或 event 等,向DUV施加激励。注意这些顶层之间是没有端口映射的,它们之间的互相调用和访问是通过层次路径名的方式来访问,上图的虚线表示层次路径名的访问。下面举例说明层次路径是如何访问的。

由于大部分人对C都有所认识,在这里作个比较,便于了解。Verilog HDL的顶层类似于C的结构体,而实例化的模块、任务、函数、变量等就是结构体里的成员,可以通过句点( . )隔开的方式访问结构体里面的每一个成员。如:顶层 harness 实例化进来的模块 BFM1 里面有一个任务SEND_DATA , 该任务可以产生激励输入到DUV,在 testcase 里调用该任务就可写为:

initial

begin

……

harness . BFM1 . SEND_DATA ( …… ) ;

end

多顶层结构的可扩展和重用性比单顶层结构强得多。层次路径的访问方式非常有用,在下一节会讲述更多的应用。

2 如何编写Testbench

1) 何时使用initial和always

initial和always 是2个基本的过程结构语句,在仿真的一开始即开始相互并行执行。通常被动的检测响应使用always语句,而主动的产生激励使用initial语句。

initial和always的区别是always 语句不断地重复执行,initial语句则只执行一次。但是,如果希望在initial里的多次运行一个语句块,怎么办?这时可以在initial里嵌入循环语句(while,repeat,for,forever 等),如:

initial

begin

forever /* 无条件连续执行*/

begin

……

end

end

其它循环语句请参考一些教材,这里不作赘述。

另外,如果希望在仿真的某一时刻同时启动多个任务,可以使用fork....join语句。例如,在仿真开始的 100 ns 后,希望同时启动发送和接收任务,而不是发送完毕后再进行接收,如下所示:

initial

begin

#100 ;

fork /*并行执行 */

Send_task ;

Receive_task ;

join

End

2) 如何作多种工作模式的遍历测试

如果设计的工作模式很多,免不了做各种模式的遍历测试,而遍历测试是需要非常大的工作量的。我们经常遇到这样的情况:很多时候,各种模式之间仅仅是部分寄存器配置值的不同,而各模式间的测试都是雷同的。有什么方法可以减轻这种遍历测试的工作量?不妨试试for循环语句,采用循环变量来传递各种模式的配置值,会帮助减少很多测试代码,而且不会漏掉每一种模式.

initial

begin

for ( i = 0 ; i < m ; i = i + 1 ) /*遍历模式1至模式m*/

for ( j = 0 ; j < n ; j = j +1 ) /*遍历子模式1至子模式n */

begin

case ( j ) /* 设置每种模式所需的配置值 */

0 : 配置值 = a ;

1 : 配置值 = b ;

2 : 配置值 = c ;

……

endcase

/*共同的测试向量*/

end

end

3) 如何加速问题定位过程

在这部分里,通过一些实际例子,介绍在出现问题时如何借助 testbench 加快问题的定位过程。

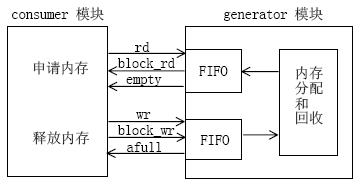

1、监测内存分配

内存分配和回收示意图

在这个例子里,假设总共有2K的内存块,希望在测试程序里监测内存分配和回收的块号是否正确,监测是否存在同一块号重复分配、重复回收的情况。设置一个2K位的变量对内存的使用情况进行记录,每一位对应一个内存块,空闲的块号记为1,被占用的块号记为0。该变量的初始值为全1,当分配一个块号出去时先判断该位是否为空闲,若是空闲则将该位设置为被占用,否则就为重复分配错误。相反,当回收一个块号时,先判断该位是否被占用,若是被占用则将该位设置为空闲,否则就为重复回收错误。程序如下:

always @(posedge Clk or negedge Rst )

begin

if ( Rst == 1'b0 )

Mem_status <= 2048 {1'b1} ;

else

begin

if ( 层次路径 . rd ) /* 监测内存分配,block_rd 是分配的内存块号*/

if ( Mem_status [ block_rd ] == 1'b1 )

Mem_status [ block_rd ] <= 1'b0 ;

else

begin

$display ( "Error! 重复分配同一内存块! ") ;

$stop ;

end

if ( 层次路径 . wr ) /* 监测内存回收,block_wr 是回收的内存块号*/

if ( Mem_status [ block_wr ] == 1'b0 )

Mem_status [ block_wr ] <= 1'b1 ;

else

begin

$display ( "Error! 重复回收同一内存块! ") ;

$stop ;

end

end

End

2、监测内部接口

如果你是位验证工程师,在做芯片级的仿真时,相信你会或曾遇到过这样的问题:在一个端口输入了激励数据,但另一端口却得不到正确的响应,而且这条路径涉及到很多模块和很多个不同设计者,为了定位问题,你可能很盲目地逐个找来设计人员,逐个模块地记录仿真波形,到解决问题时,可能几天已经过去了。

我们都知道,如果问题定位在越小的范围,就越便于解决问题。所以,我们可以把模块接口间交换的数据记录到文件里,当出现问题时,就可以查看各接口的记录数据,看问题到底出现在哪个区间,简单地查看记录文件后,你就明确该找那位designer来解决问题。

3、记录有用的DEBUG信息

记录有用的debug信息,输出到标准的I/O设备上(屏幕或文件),会给你的debug带来很大的便利,由上面的例子也可见一斑,在检测到有错误时也可使用$stop令仿真停下来。

值得注意的是,UNIX系统只有32个I/O,每个输出文件占用1个I/O设备号,其中第1个是屏幕显示,设备号是32'b1,其它I/O设备号由输出文件占用,一个信息可同时输出到屏幕和文件,如:

initial

begin

Ptr_log = $fopen ("log.txt ") ; /* 创建一个文件,获得文件指针 */

Ptr_log = Ptr_log | 32'b1 ; /* 指针同时指向 log.txt 文件和屏幕 */

end

always @(……)

begin

$fwrite ( Ptr_log, "useul message ",……) ; /*信息除了记录到文件同时,还显示到屏幕*/

……

end

虽然记录文件会给debug带来很多便利,但文件操作会降低仿真的速度,因此应当适可而止。

另外写文件通常有2种方式,不同的仿真工具有所差异。一种是每写一个字节打开关闭一次文件,如Verilog-XL。另一种是先把字符暂存到内存,等累积到一定数量(如8K字节)后再通过DMA方式把字符从内存写到文件,如Verilog-NC。因此,后一种方式就大大地降低了文件的操作次数,有利于提高仿真速度。

-

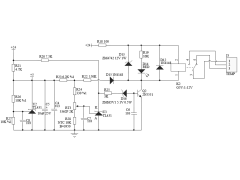

一款高温报警电路2024年11月13日 81

-

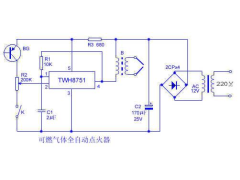

可燃气体全自动点火器2012年09月22日 76

-

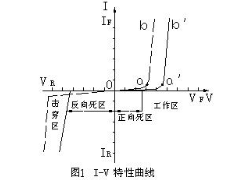

LED参数与特性2012年09月18日 118

-

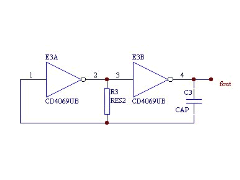

RC振荡电路的几种接法2012年09月10日 221

-

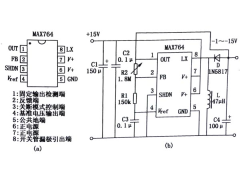

MAX764极性反转电路2012年08月24日 47

-

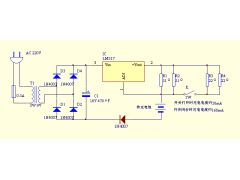

实用恒流充电器2012年08月18日 175

-

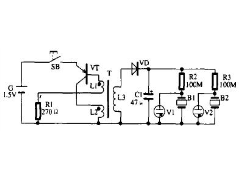

电子催眠器制作2012年08月15日 72

-

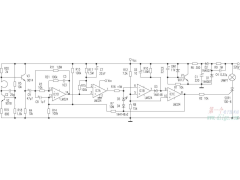

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4875

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499