基于VHDL语言的 IP 核验证

2012-06-02

14

摘要:探讨了IP核的验证与测试的方法及其和VHDL语言在IC设计中的应用.并给出了其在RISC8框架CPU核中的下载实例 引言 在IC(integrated circuit.集成电路)发展到超大规模阶段的今天,基于IP(Intellectual Property,知识产权)核的IC设计及其再利用是保证SoC(system onchip,片上系统)开发效率和质量的重要手段。如果能对IP ..

[查看全文]

verilog的键盘源码keypad—有去抖功能

2012-06-02

11

下面是转的一个源码,俺没有细看,有兴趣的看看,讲讲如何 // author: Dandy Nee // mail:dandynee@yeah.net // module: HW KeyScan Module // version:0.1 // ************************** // all functions are provided as if okay // run at your own risk // ************************** // // problem:there is one keyva ..

[查看全文]

TEXTIO及其在VHDL仿真中的应用

2012-06-02

于红旗

16

TEXTIO 在VHDL 仿真与磁盘文件之间架起了桥梁,使用文本文件扩展VHDL 的仿真功能。本文介绍TEXTIO 程序包,以一个加法器实例说明TEXTIO 的使用方法,最后使用ModelSim 对设计进行仿真,并分析仿真结果。 在对VHDL 源程序进行仿真时, 由于有的输入输出关系仅仅靠输入波形或编写testbench 中的信号输入是难以验证结果正确 ..

[查看全文]

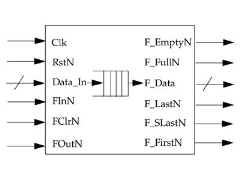

可综合的Verilog FIFO存储器

2012-06-02

12

可综合的Verilog FIFO存储器 This example describes a synthesizable implementation of a FIFO. The FIFO depth and FIFO width in bits can be modified by simply changing the value of two parameters, `FWIDTH and `FDEPTH. For this example, the FIFO depth is 4 and the FIFO width is 32 bits. The input/output p ..

[查看全文]

fir滤波器的Verilog程序

2012-06-02

35

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date:17:01:38 10/09/06 // Design Name: // Module Name:ppeifir // Project Name: // Target Device: // Tool versions: // Description:用Verilog编写的fir滤波器程 ..

[查看全文]

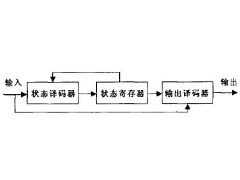

Verilog HDL代码描述对状态机综合的研究

2012-06-02

李玲 王祖强 陈东海

8

1 引言 Verilog HDL作为当今国际主流的HDL语言,在芯片的前端设计中有着广泛的应用。它的语法丰富,成功地应用于设计的各个阶段:建模、仿真、验证和综合等。可综合是指综合工具能将Verilog HDL代码转换成标准的门级结构网表,因此代码的描述必须符合一定的规则。大部分数字系统都可以分为控制单元和数据单元两个部分,控制单元 ..

[查看全文]

基于VHDL的异步串行通信电路设计

2012-06-02

李刚强

19

1 引 言 随着电子技术的发展,现场可编程门阵列 FPGA和复杂可编程逻辑器件CPLD的出现,使得电子系统的设计者利用与器件相应的电子CAD软件,在实验室里就可以设计自己的专用集成电路ASIC器件。这种可编程ASIC不仅使设计的产品达到小型化、集成化和高可靠性,而且器件具有用户可编程特性,大大缩短了设计周期,减少了设计费 ..

[查看全文]

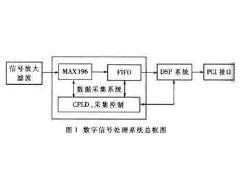

用Verilog HDL设计自动数据采集系统

2012-06-02

11

随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。从电子CAD、电子CAE到电子设计自动化(EDA ..

[查看全文]

我的仿真工作流程(Verilog/Modelsim+Debussy)

2012-06-02

29

这是献给大家的第二篇,文章详细说明了本人近一年来,自己摸索出来的一套仿真工作流程。接触过Modelsim这类软件的朋友可能都会感觉上手比较困难,原因有二:一、对仿真机制不了解,对基于source+testbench的工作流程不熟悉(大多数朋友接触FPGA仿真可能以waveform的方式);二、对软件的安装和使用不熟悉,Modelsim软 ..

[查看全文]

浅谈VHDL/Verilog的可综合性以及对初学者的一些建议

2012-06-02

13

一、HDL不是硬件设计语言 过去笔者曾碰到过不少VHDL或Verilog HDL的初学者问一些相似的问题,诸如如何实现除法、开根号,如何写循环语句等等。在这个论坛上,也时常能看到一些网友提出这一类的问题。 对于这些问题,首先要明确的是VHDL和Veriglog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。HDL是Har ..

[查看全文]

VHDL的CRC编码器的设计

2012-06-02

郑春来

32

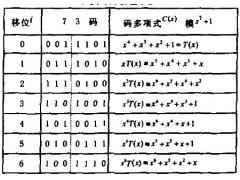

CRC码是线性分组码的一个重要子集,它是为了保证通信系统中的数据传输可靠性而采取的信道编码技术。CRC码除了具有分组码的线性外,还具有循环性,其码字结构一般用符号(n,k)表示,其中,n是该码组中的码元数,k是信息码位数,r=n-k是监督码元位数。循环码具有许多特殊的代数性质,这些性质有助于按照要求的纠错能力系统地 ..

[查看全文]

VHDL设计的消抖与滤波

2012-06-02

15

在同一块电路板上,由于信号线的走线过长而产生的高频毛刺我们可以通过在接近输入端串联一个100欧左右的电阻来滤除。但是对于板外信号,或者板内其他干扰造成较大的抖动时只好采用积分电路来滤波,即串一个电阻还要并一个电容接地。 同样在VHDL中我们可以采用类似的办法,对于小于触发器建立时间的毛刺可以用时钟打一下实现 ..

[查看全文]

推荐文章

最新文章

热门文章