Verilog 16位超前进位加法器源码

2012-10-07

17

module cla16 (a,b,s);//top module 含有四个4 位超前进位加法器子模块 input [15:0] a, b; output [15:0] s; wire pp4,pp3,pp2,pp1; wire gg4,gg3,gg2,gg1; wire [14:0] Cp; wire [15:0] p,g; claslice i1 (p[3],p[2],p[1],p[0],g[3],g[2],g[1],g[0],1'b0,Cp[2],Cp[1],Cp[0],pp1,gg1); claslice i2 (p[7],p[6],p[5], ..

[查看全文]

Verilog HDL设计练习进阶(六)

2012-10-06

9

练习六. 在Verilog HDL中使用函数 目的:掌握函数在模块设计中的使用。 与一般的程序设计语言一样,Veirlog HDL也可使用函数以适应对不同变量采取同一运算的操作。Veirlog HDL函数在综合时被理解成具有独立运算功能的电路,每调用一次函数相当于改变这部分电路的输入以得到相应的计算结果。 下例是函数调用的一个简单示范,采用 ..

[查看全文]

在PLD开发中提高VHDL的综合质量

2012-10-05

石俊斌 林辉

13

引 言 随着计算机与微电子技术的发展,电子设计自动化EDA(Electronic Design Automation)和可编程逻辑器件PLD(Programmable Logic Device)的发展都非常迅速,熟练地利用EDA软件进行PLD器件开发已成为电子工程师必须掌握的基本技能。先进的EDA工具已经从传统的自下而上的设计方法改变为自顶向下的设计方法,以硬件描 ..

[查看全文]

CONCEPTHDL传入ALLEGRO中参数快速参考

2012-10-04

14

许多设计师一般是采用直接在原理图上加注高速布线要求的文字说明以通知PCB设计人员注意这些要求。如果设计是用CONCEPTHDL输入的,可以直接对网线加上相应的约束参数和其要求数值。这样设计流程变得流畅,而且可以通过设计同步检查来方便地检查布线是否满足了您的设计要求。下面就这些可以由CONCEPTHDL传入ALLEGRO的 ..

[查看全文]

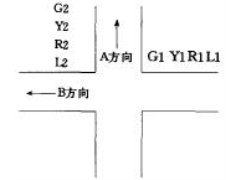

基于Verilog HDL语言的带左转复杂交通灯设计

2012-07-22

郭长辉 王思明

18

1 引言 EDA技术是依靠功能强大的电子计算机,在EDA工具软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动地完成逻辑编辑、化简、分割、综合、优化和仿真,直至下载到可编程逻辑器件CPLD/FPGA或专用集成电路ASIC(Application Specific Integrated Circuit)芯片中 ..

[查看全文]

N.5分频的VHDL实现

2012-07-22

38

这种分频需要对输入时钟进行操作。基本的设计思想:对于进行n+0.5分频,首先进行模n的计数,在计数到n-1时,输出时钟赋为‘1’,回到计数0时,又赋为0,因此,可以知道,当计数值为n-1时,输出时钟才为1,因此,只要保持计数值n-1 为半个输入时钟周期,即实现了n+0.5分频时钟,因此保持n-1为半个时钟周期即是 ..

[查看全文]

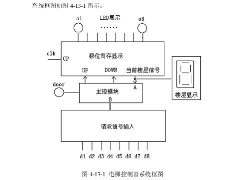

Verilog电梯控制器设计

2012-06-25

14

设计一个八层楼房自动电梯控制器,用八个 LED显示电梯行进过程,并有数码管显示电梯当前所在楼层位置,在每层电梯入口处设有请求按钮开关,请求按钮按下则相应楼层的LED 亮。 用 CLK脉冲控制电梯运动,每来一个 CLK脉冲电梯升(降)一层。电梯到达有请求的楼层后,该层次的指示灯灭,电梯门打开(开门指示灯亮),开门 5 秒 ..

[查看全文]

HDL编码风格与编码指南

2012-06-24

15

作者:徐欣 博士 孙广富 博士原文出自e元素科技网站Rev. 0.1June 30,2002第一部分:说明 1.准则的重要程度分三个层次:好的经验 -- 表明这条规则是一般情况下比较好的经验,在大多数的情况下要遵循,在特殊情况下可以突破这一规则。推荐 -- 推荐这一规则,在遵循这一规则的条件下,一般不会出现问题;强烈推荐 -- 表示严格规 ..

[查看全文]

自动售货机控制系统VHDL有限状态机实现

2012-06-13

赖义汉

12

1 引言 有限状态机FSM(Finite State Machine)及其设计技术是实用数字系统设计中实现高效率、高可靠逻辑控制的重要途径。传统的状态机设计方法需进行繁琐的状态分配、绘制状态表、化简次态方程等,而利用VHDL可以避免这些繁琐的过程,直接利用状态转换图进行状态机的描述,所有的状态均可表达为CASE_WHEN结构中的一条CA ..

[查看全文]

Verilog HDL设计练习进阶(五)

2012-06-11

12

练习五. 用always块实现较复杂的组合逻辑电路 目的: 1.掌握用always实现组合逻辑电路的方法; 2.了解assign与always两种组合逻辑电路实现方法之间的区别。 仅使用assign结构来实现组合逻辑电路,在设计中会发现很多地方会显得冗长且效率低下。而适当地采用always来设计组合逻辑,往往会更具实效。已进行的范例和练习中,我们 ..

[查看全文]

verilog HDL设计练习进阶(一)

2012-06-02

6

练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法。 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 模块源 ..

[查看全文]

verilog设计经验

2012-06-02

10

一、组合逻辑 1、敏感变量的描述完备性 Verilog中,用always块设计组合逻辑电路时,在赋值表达式右端参与赋值的所有信号都必须在 always @(敏感电平列表)中列出,always中if语句的判断表达式必须在敏感电平列表中列出。如果在赋值表达式右端引用了敏感电平列表中没有列出的信号,在综合时将会为没有列出的信号隐含地产生一个透 ..

[查看全文]

推荐文章

最新文章

热门文章