基于FPGA 实现PCI总线控制器

2013-01-31

赵敏 任作新

10

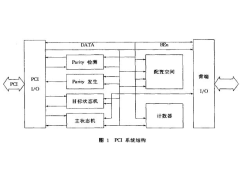

摘要:介绍用FPGA 实现PCI总线的方法.方法根据数字电路设计的自上而下的设计方法,用VHDL 实现,并在Xilinx的SpartenII器件中进行验证.结果与结论结果表明:用FPGA 实现PCI总线是经济可行的. PCI的含义为周边器件互连(Peripheral Component Interconnection).PCI总线规范1.0由Int口公司开发,现由一个工业厂商协会管 ..

[查看全文]

FPGA异步时钟设计中的同步策略

2013-01-30

廖艳 王广君 高杨

5

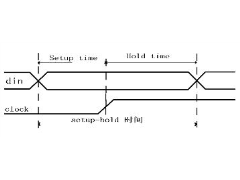

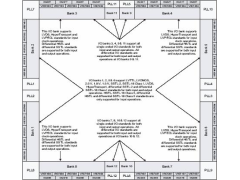

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。本文总结出了几种同步 ..

[查看全文]

甚于ARM和FPGA的全彩独立视频LED系统

2013-01-27

胡月华 谢彦峰 张忠林

29

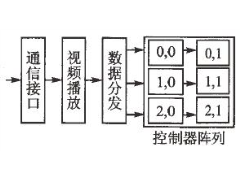

目前,显示屏按数据的传输方式主要有两类:一类是采用与计算机显示同一内容的实时视频屏;另一类为通过USB、以太网等通信手段把显示内容发给显示屏的独立视频源显示屏,若采用无线通信方式,还可以随时更新显示内容,灵活性高。此外,用一套嵌入式系统取代计算机来提供视频源,既可以降低成本,又具有很高的可行性和灵活性, ..

[查看全文]

使用SignalTap II逻辑分析仪调试FPGA

2013-01-24

8

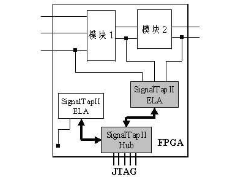

摘 要 :本文介绍了可编程逻辑器件开发工具Quartus II 中SingalTap II 嵌入式逻辑分析器的使用,并给出一个具体的设计实例,详细介绍使用SignalTap II对FPGA调试的具体方法和步骤。 关键字 : SignalTap;硬件调试;FPGA 1 概述 随着FPGA容量的增大,FPGA的设计日益复杂,设计调试成为一个很繁重的任务。为了使得设计尽快投入市 ..

[查看全文]

使用 FPGA 控制 VGA 显示

2013-01-24

10

显示器因为其输出信息量大,输出形式多样等特点已经成为现在大多数设计的常用输出设备。在FPGA的设计中可以使用很少的资源,就产生VGA 各种控制信号。这个示例在 RHicSP2200BFPGA开发板/学习板上使用VGA接口在显示器上显示了文字以及简单的图形,可以作为VGA 显示设计的参考,如果在使用这个例子的过程中有任何问题都可 ..

[查看全文]

FPGA管脚分配需要考虑的因素

2013-01-23

5

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL 验证与验证板设计必须是同步进行的,在验证代码出来时验证的单板也必 ..

[查看全文]

FPGA逻辑设计注意事项列表

2013-01-23

潘登

8

这是一个在逻辑设计中注意事项列表,由此引起的错误常使得设计不可靠或速度较慢,为了提高设计性能和提高速度的可靠性,必须确定设计通过所有的这些检查。 可靠性 1. 为时钟信号选用全局时钟缓冲器BUFG! 不选用全局时钟缓冲器的时钟将会引入偏差。 2. 只用一个时钟沿来寄存数据 使用时钟的两个沿是不可靠的,因为时钟的某沿或者 ..

[查看全文]

基于FPGA/CPLD设计与实现UART(VHDL)

2013-01-20

24

1 引言 由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA/CPLD和嵌入系统的多种模式。可以说EDA产业已经成为电子信息类产品的支柱产业。EDA之所以能蓬勃发展的关键因素之一就是采用了硬件描述语言(H ..

[查看全文]

FPGA/CPLD实验教程一(点亮LED)

2013-01-19

抽烟的鱼

166

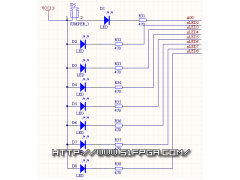

1. 实验要求及目的: 点亮发光二极管。通过这个实验,熟悉CPLD/FPGA开发软件的使用方法和开发流程及Verilog HDL 的编程方法。通过这个实验可以实际使用一下Quartus II软件,一通百通,下次就不讲那么详细了:) 使用软件:Quartus II 5.0。 2. 硬件原理图: 这个是我自己制作的开发板上的LED的原理图,一共有8个,IO和别的共 ..

[查看全文]

影响FPGA设计中时钟因素的探讨

2013-01-19

30

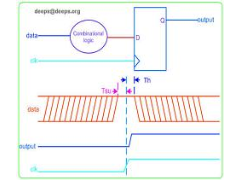

时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错;因而明确FPGA设计中决定系统时钟的因素,尽量较小时钟的延时对保证设计的稳定性有非常重要的意义。 1.1 建立时间与保持时间 建立时间(Tsu:set up time)是指在时钟 ..

[查看全文]

用FPGA实现实时视频处理

2013-01-15

13

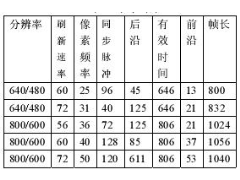

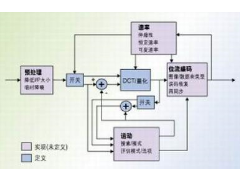

随着数字融合的进一步发展,系统的设计和实现需要更大的灵活性,以解决将完全不同的标准和要求集成为同类产品时引发的诸多问题。本文介绍 FPGA在视频处理中的应用,与ASSP和芯片组解决方案相比,FPGA可根据当前(中国)设计工程师的实际需求提供不同层次的灵活性,并保持明显优于传统DSP的性能。 实时视频处理对系统性能的 ..

[查看全文]

基于FPGA的SOC系统中的串口设计

2013-01-14

葛锐 欧钢

13

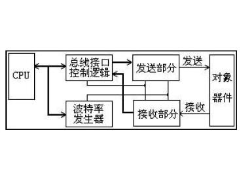

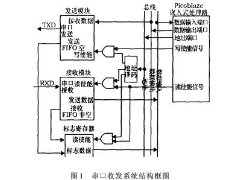

1 概述 在基于FPGA的SOC设计中,常使用串口作为通信接口,但直接用FPGA进行串口通信数据的处理是比较繁杂的,特别是直接使用FPGA进行串口通信的协议的解释和数据打包等处理,将会消耗大量的FPGA硬件资源。为简化设计,降低硬件资源开销,可以在FPGA中利用IP核实现的嵌入式微处理器来对串口数据进行处理。 本文中的设计采用了 ..

[查看全文]

推荐文章

最新文章

热门文章