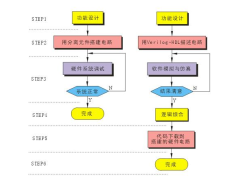

SDRAM控制器软核的Verilog设计

2012-11-23

20

目前,在很多通信芯片及系统的开发中,常常需要用到存储容量大、读写速度高的存储器。在各种随机存储器件中,SDRAM 的价格低、体积小、速度快、容量大,是比较理想的器件。但是,与SRAM相比较,SDRAM的控制逻辑复杂,使用很不方便。为了解决这个矛盾,需要设计专用的SDRAM控制器,使系统用户象使用SRAM一样方便的使 ..

[查看全文]

Verilog学习心得

2012-11-23

10

因为Verilog是一种硬件描述语言,所以在写Verilog语言时,首先要有所要写的module在硬件上如何实现的概念,而不是去想编译器如何去解释这个module. 比如在决定是否使用reg定义时,要问问自己物理上是不是真正存在这个register, 如果是,它的clock是什么? D端是什么?Q端是什么?有没有清零和置位?同步还是异步?再比如上面 ..

[查看全文]

verilog HDL 的阻塞和非阻塞语句分析

2012-11-14

e人

13

在FPGA设计中完全透视verilog HDL 的阻塞和非阻塞语句,是个人在verilog HDL运用中的一些心得体会。 阻塞和非阻塞语句作为verilog HDL语言的最大难点之一,一直困扰着FPGA设计者,即使是一个颇富经验的设计工程师,也很容易在这个点上犯下一些不必要的错误。阻塞和非阻塞可以说是血脉相连,但是又有着本质的差别。理解不清 ..

[查看全文]

Verilog HDL设计练习进阶(四)

2012-11-08

8

练习四. 设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别 目的:1.明确掌握阻塞赋值与非阻塞赋值的概念和区别; 2.了解阻塞赋值的使用情况。 阻塞赋值与非阻塞赋值,在教材中我们已经了解了它们之间在语法上的区别以及综合后所得到的电路结构上的区别。在always块中,阻塞赋值可以理解为赋值语句是顺序执行的,而非阻塞赋值可以 ..

[查看全文]

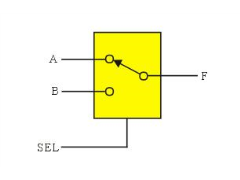

典型逻辑电路的Verilog-HDL描述

2012-11-06

常晓明 李媛媛

10

Verilog-HDL与CPLD/FPGA设计应用讲座 第 5 讲 典型基本逻辑路的Verilog-HDL描述 5.1 数据选择器 5.2 编码器 5.3 同步RS触发器 5.4 带有复位端的同步D触发器 本讲列举几个典型又简单的基本逻辑电路的Verilog-HDL描述。需要说明,仅有本讲的知识还不能具备用Verilog-HDL描述逻辑电路和系统的基本功,但却可以通过几个例子了解 ..

[查看全文]

Verilog-HDL与CPLD/FPGA设计

2012-10-31

常晓明

44

Verilog-HDL与CPLD/FPGA设计应用讲座 第 1 讲 Verilog-HDL与CPLD/FPGA设计 1.1 从模拟世界到数字世界 1.2 数字电路的不同设计过程 1.3 用HDL描述数字电路 1.4 HDL有几种? 1.5 硬件实现的承担者---CPLD/FPGA 1.6 Xilinx公司的CPLD--XC9500系列 1.7 结语 1.1 从模拟世界到数字世界 在70年代初期,家用电子产品末过于晶体管 ..

[查看全文]

让Verilog仿真状态机时可以显示状态名

2012-10-31

RickySu

32

Situation: 我们平时使用Verilog进行状态机编码时,通常使用parameter对状态名进行定义,这样写Case语句的时候就不会对这一串10摸不着头脑。可是通常这样做的话,在Modelsim里看到的还是一串10,使排错非常困难,特别是在用OneHot编码的时候,就看到一串0中间的一个1 #_# 简直要疯掉。 Question: 我们可不可以像VHDL一样 ..

[查看全文]

用Verilog HDL实现I2C总线功能

2012-10-16

13

摘要: 简述了I2C总线的特点;介绍了开发FPGA时I2C总线模块的设计思想;给出并解释了用Verilog HDL实现部分I2C总线功能的程序,以及I2C总线主从模式下的仿真时序图。 关键词: I2C总线 FPGA Verilog HDL 时序 开发FPGA时,利用EDA工具设计芯片实现系统功能已经成为支撑电子设计的通用平台,并逐步向支持系统级的设计方向发 ..

[查看全文]

Verilog常见moduel接口定义错误

2012-10-13

14

过去见过不少新手在这方面出错,而且查不出原因,感觉有必要给大家提个醒。 Verilog中moduel的接口类型主要有in、out和inout三种,出错的主要在in和out的定义上。常常我们把接口定义成wire或reg两种数据类型,而出错的主要原因在于不少新手不知道reg类型的含义。 强调一下,定义为reg类型的数据,其描述的是一个register的输 ..

[查看全文]

Verilog 编码原则

2012-10-13

8

规则 #1: 建立时序逻辑模型时,采用非阻塞赋值语句。 规则 #2: 建立latch模型时,采用非阻塞赋值语句。 规则 #3: 在always块中建立组合逻辑模型时,采用阻塞赋值语句。 规则 #4: 在一个always块中同时有组合和时序逻辑时时,采用非阻塞赋值语句。 规则 #5: 不要在一个always块中同时采用阻塞和非阻塞赋值语句。 规则 #6: 同一个变 ..

[查看全文]

Verilog 16位超前进位加法器源码

2012-10-07

17

module cla16 (a,b,s);//top module 含有四个4 位超前进位加法器子模块 input [15:0] a, b; output [15:0] s; wire pp4,pp3,pp2,pp1; wire gg4,gg3,gg2,gg1; wire [14:0] Cp; wire [15:0] p,g; claslice i1 (p[3],p[2],p[1],p[0],g[3],g[2],g[1],g[0],1'b0,Cp[2],Cp[1],Cp[0],pp1,gg1); claslice i2 (p[7],p[6],p[5], ..

[查看全文]

Verilog HDL设计练习进阶(六)

2012-10-06

9

练习六. 在Verilog HDL中使用函数 目的:掌握函数在模块设计中的使用。 与一般的程序设计语言一样,Veirlog HDL也可使用函数以适应对不同变量采取同一运算的操作。Veirlog HDL函数在综合时被理解成具有独立运算功能的电路,每调用一次函数相当于改变这部分电路的输入以得到相应的计算结果。 下例是函数调用的一个简单示范,采用 ..

[查看全文]

推荐文章

最新文章

热门文章