FPGA/CPLD实验教程四(基本的逻辑门实验)

2012-11-19

抽烟的鱼

28

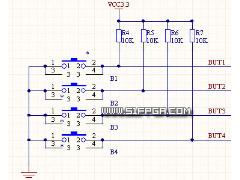

1. 实验要求及目的: 前面三个实验我们都只用到了LED,也就是输出。但是我们做的东西多半都是需要人机交互的,所以不能光是有输出,还应该有输入(其实前面也用到了输入,那就是时钟)。这个实验我们会用到按钮,通过按钮输入,判断逻辑,然后利用LED来显示出来逻辑输出结果。 这个实验主要是体会一下输入的用法,难度比较小 ..

[查看全文]

基于FPGA/CPLD和USB技术的无损图像采集卡

2012-11-16

姚聪

28

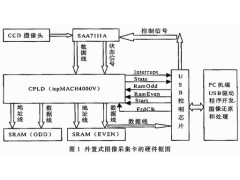

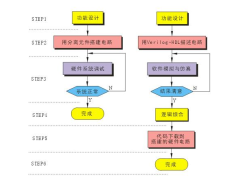

现场图像采集技术发展迅速,各种基于ISA、PCI等总线的图像采集卡已经相当成熟,结合课题设计了一款USB外置式图像采集卡。该图像采集卡已成功应用于一个图像处理和识别的项目中,由于图像信号不经过压缩处理,对后续处理没有任何影响,因此图像处理和识别的效果比一般的图像采集卡要好,满足了特殊场合的特殊需要。 1 外置式 ..

[查看全文]

FPGA/CPLD实验教程三(流水灯)

2012-11-07

抽烟的鱼

151

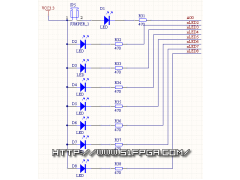

1. 实验要求及目的: 这次的实验我们要做的是流水灯,顾名思义就是要LED象水一样的点亮(好像有点不怎么顾名思义啊),这样说吧,就是先单独点亮第一个,然后点亮第二个(这个时候有两个灯亮了),然后…… 这一个实验主要教会大家一个比较方便的锁定引脚的办法,另外就是使用移位运算符。 使用软件:Quartus II 5.0 ..

[查看全文]

基于CPLD 的三相多波形函数发生器设计

2012-11-07

尹佳喜 尹 仕

14

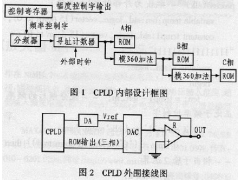

摘要:介绍了基于可编程逻辑器件CPLD 和直接数字频率合成技术(DDS)的三相多波形函数发生器的基本原理,并在此基础上给出了基于CPLD 的各模块设计方法及其VHDL 源程序。 关键词:CPLD;直接数字频率合成;函数发生器;VHDL 1 引言 直接数字频率合成(Direct Digital Synthesis,DDS)是20世纪60年代末出现的第三代频率合成 ..

[查看全文]

基于CPLD的单片机PCI接口设计

2012-11-05

吕 刚 周爱国

15

摘要:详细阐述一种利用CPLD 实现的8 位单片机与PCI 设备间的通信接口方案,给出用ABEL HDL 编写的主要源程序。该方案在实践中检验通过。 关键词:单片机 CPLD PCI 8 位单片机在嵌入式系统中应用广泛,然而让它直接与PCI 总线设备打交道却有其固有缺陷。8 位单片机只有16 位地址线,8 位数据端口,而PCI 总线2.0 规范中,除了 ..

[查看全文]

Verilog-HDL与CPLD/FPGA设计

2012-10-31

常晓明

44

Verilog-HDL与CPLD/FPGA设计应用讲座 第 1 讲 Verilog-HDL与CPLD/FPGA设计 1.1 从模拟世界到数字世界 1.2 数字电路的不同设计过程 1.3 用HDL描述数字电路 1.4 HDL有几种? 1.5 硬件实现的承担者---CPLD/FPGA 1.6 Xilinx公司的CPLD--XC9500系列 1.7 结语 1.1 从模拟世界到数字世界 在70年代初期,家用电子产品末过于晶体管 ..

[查看全文]

用VHDL在CPLD上实现串行通信

2012-10-31

17

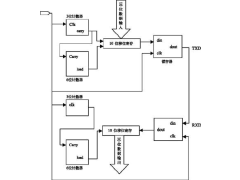

随着EDA技术得发展,CPLD已经在许多方面得到了广泛应用,而串行通信是实现远程测控的重要手段。本文利用VHDL语言在CPLD上实现了串行通信,完全可以脱离单片机使用,克服了单片机的许多缺点。 串口结构及内容 本设计所采用的是异步通信方式,可以规定传输的一个数据是10位,其中最低位为启动位(逻辑0低电平),最高位为停止位(逻 ..

[查看全文]

CPLD 120MHz高速A/D采集设计

2012-10-16

徐法东 翟正军

78

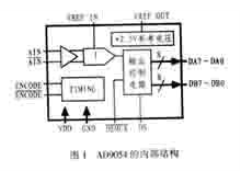

摘要:介绍了一种基于复杂可编程逻辑器件(CPLD)的120MHz高速A/D采集卡的设计方法。给出了这种采集卡的硬件原理电路和主要的软件设计思路。采用该设计方法设计的数据采集卡具有包括负延迟触发等多种触发方式,具有体积小,工作可靠,控制简单等特点。 关键词:高速A/D;CPLD;负延迟触发;EPM7128;AD9054 高速A/ ..

[查看全文]

基于CPLD的一种容错状态机的设计

2012-10-15

刘华伟 郭创

16

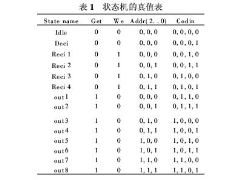

状态机是一种十分重要的时序电路,常用于描述数字系统的控制单元,在数字系统有着广泛的应用,如步进电机、数据存储器的读写、总线控制器等。本文结合具体课题;采用ALTERA的CPLD器件EPM7032实现了一种容错的状态机;采用VHDL语言编程,实际使用效果良好,不仅调试方便,而且增加了系统配置的灵活性,大大缩短了系统开发周期。 ..

[查看全文]

CPLD驱动数码显示电路

2012-10-14

11

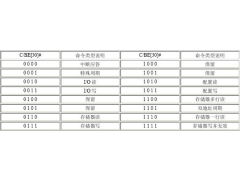

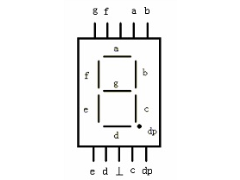

1.1 显示原理: 八段数码显示管如图1.1 所示,八段数码管每一段为一发光二极管,共有a~g 以及小数点dp 八个发光二极管。将八段数码管中的每个二极管的阴极并联在一起,组成公共阴极端。这样把共阴极管脚接地,此时哪个管脚输入高电平,对应发光二极管就被点亮。 图 1.1 八段数码显示管 CL5461AS 数码管管脚图如图1.2 所示,它 ..

[查看全文]

在PLD开发中提高VHDL的综合质量

2012-10-05

石俊斌 林辉

13

引 言 随着计算机与微电子技术的发展,电子设计自动化EDA(Electronic Design Automation)和可编程逻辑器件PLD(Programmable Logic Device)的发展都非常迅速,熟练地利用EDA软件进行PLD器件开发已成为电子工程师必须掌握的基本技能。先进的EDA工具已经从传统的自下而上的设计方法改变为自顶向下的设计方法,以硬件描 ..

[查看全文]

I2C总线通讯接口器件的CPLD实现

2012-10-03

15

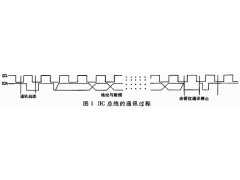

I2C总线是PHILIPS公司开发的一种简单、双向、二线制、同步串行总线。它只需两根线(串行时钟线和串行数据线)即可在连接于总线上的器件之间传送信息。该总线是高性能串行总线,具备多主机系统所需要的裁决和高低速设备同步等功能,应用极为广泛。 目前市场上虽然有专用IIC总线接口芯片,但是地址可选范围小、性能指标固定、功 ..

[查看全文]

推荐文章

最新文章

热门文章