FPGA四阶IIR数字滤波器实现

2012-06-02

10

常用的数字滤波器有FIR数字滤波器和IIR数字滤波器。FIR数字滤波器具有精确的线性相位特性,在信号处理方面应用极为广泛,而且可以采用事先设计调试好的FIR数字滤波器IPCore来完成设计,例如Altera公司提供的针对Altera系列可编程器件的MegaCore,但是需要向Altera公司购买或申请试用版。另外,对于相同的设计指 ..

[查看全文]

基于MATLAB的数字滤波器性能分析

2012-06-02

柴政 刘亮

19

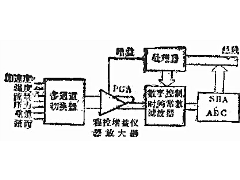

近年来,随着MATLAB的功能日益便捷和完善,信号处理以及数字滤波器设计得到了广泛应用.比如基础的IIR(无限长响应)滤波器和FIR(有限长响应)滤波器都由以前的传统解析设计向程序开发、函数调用,甚至直接使用面向对象的GUI设计工具转变.整个滤波器的设计得以变得简单高效. 关于基于MATLAB的数字滤波器设计的文献书籍有 ..

[查看全文]

基于FPGA的IIR数字滤波器的快捷设计

2012-06-02

童位理

17

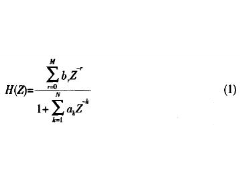

IIR数字滤波器在很多领域中都有着广阔的应用。与FIR数字滤波器相比,IIR数字滤波器可以用较低的阶数获得较高的选择性,而且所用存储单元少。经济效率高。一个N阶IIR数字滤波器的系统函数为: 其线性常系数差分方程为: 用FPGA实现滤波的基本思想就是基于式(2)来实现的。如果知道了系统的输入序列(滤波器的输入),那么,只要 ..

[查看全文]

IIR数字滤波器的FPGA实现

2012-06-02

魏国华

8

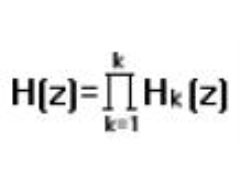

摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此设计扩展性好,便于调节滤波器的性能,可以根据不同的要求在不同规模的FPGA上加以实现。 IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同 ..

[查看全文]

基于流水线技术的并行高效FIR滤波器设计

2012-06-02

刘刚 林志远 王毅增

11

数字滤波器可以滤除多余的噪声,扩展信号频带,完成信号预调,改变信号的特定频谱分量,从而得到预期的结果。数字滤波器在DVB、无线通信等数字信号处理中有着广泛的应用。在数字信号处理中,传统滤波器通过高速乘法累加器实现,这种方法在下一个采样周期到来期间,只能进行有限操作,从而限制了带宽。现实中的信号都是以一定 ..

[查看全文]

基于PSpice的四阶有源带通滤波器的统计优化设计

2012-06-02

汪汉新 喻胜辉

23

PSpice作为功能强大的EDA电子仿真软件,不仅能对电路进行基本性能的分析和验证,还可以进行优化分析和综合统计分析,实现从电路的设计、性能分析、参数优化到电路板制作的全过程,因此它在电路的设计中得到广泛地应用.本文针对电子产品在实际生产过程中由于元器件参数值的随机分布性而造成产品合格率下降的问题,在分析PS ..

[查看全文]

基于FPGA的FIR滤波器的实现

2012-06-02

郭继昌 向 晖 滕建辅 李香萍

22

摘 要: 提出了一种采用现场可编程门阵列器件 FPGA并利用窗函数法实现线性 FIR数字滤波器硬件电路的方案,并以一个十六阶低通 FIR数字滤波器电路的实现为例说明了利用Xilinx公司 XC4000系列芯片的设计过程。设计的电路通过软件程序进行了验证和硬件仿真,结果表明电路工作正确可靠,能满足设计要求。 关键词: FPGA FIR数字滤 ..

[查看全文]

推荐文章

最新文章

热门文章