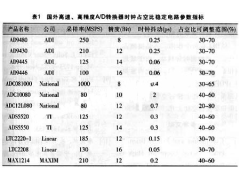

高精度高速A/D转换器时钟稳定电路设计

2013-04-01

65

进入21世纪后,人类社会已全面进入信息时代,信息产业成为了现代社会最重要的支柱和最主要的产业,伴随着半导体技术、数字信号处理技术及通信技术的飞速发展,A/D、D/A转换器近年也呈现高速发展趋势,而随着高速、高精度A/D转换器(ADC)的发展,尤其是能直接进行中频采样的高分辨率数据转换器的上市,对稳定的采样时钟的 ..

[查看全文]

基于PCB 仿真的高速时钟电路设计研究

2013-03-29

张艳丽 安琪 王砚方

31

1 引言 在目前正进行的北京正负电子对撞机二期升级改造工程(BECPII) 中,北京谱仪(BESIII) 的飞行时间(Time of Flight ,简称:TOF) 读出电子学需要对一种具有25ps 分辨率的数据驱动型时间测量器件- HPTDC(High Performance TDC) 进行性能测试。为此,我们设计了一种具有更高精度的专用高精度信号发生器。由于时钟电路是整个高 ..

[查看全文]

如何实现高速时钟信号的差分布线?

2013-03-23

15

[提问] 在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线? [解答] 信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠 ..

[查看全文]

时钟芯片DS1302 的汇编和C51程序

2013-03-18

24

时钟芯片DS1302 的keil c程序 ;********************************************************************* ; 公司名称: ; 模块名称:DS1302.a51 ; 功能:实时时钟模块时钟芯片型号:DS1302 ; 说明:(修改版) ; 程序设计:zhaojunjie ; 设计时间:2002.05.04 ; 版 本 号:20020504 ;***************************** ..

[查看全文]

ucos ii中的时钟中断技术研究

2013-02-23

29

1 系统中断与时钟节拍 1.1 系统中断 中断是一种硬件机制,用于通知CPU有个异步事件发生了。中断一旦被系统识别,CPU则保存部分(或全部)现场(context),即部分(或全部)寄存器的值,跳转到专门的子程序,称为中断服务子程序(ISR)。中断服务子程序做事件处理,处理完成后执行任务调度,程序回到就绪态优先级最高的任务开始运 ..

[查看全文]

GPS高精度的时钟的设计和实现

2013-02-16

13

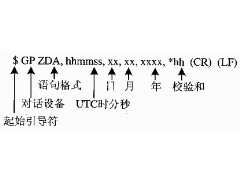

摘要:介绍采用GPS、OEM接收板来实现精密时钟系统的设计思路和方法,给出基本的硬件电路和软件流程。 1 概述 GPS(Global Positioning System)全球定位系统是利用美国的24颗GPS地址卫星所发射的信号而建立的导航、定位、授时的系统。美国==已承诺,在今后相当长的一段时间内,GPS系统将向全世界免费开放。目前,GPS系统 ..

[查看全文]

CCS中如何看程序运行的时钟周期

2013-02-08

12

1.进入CCS环境,装载已有工程,并load生成的.out文件,并找到要察看代码执行周期的代码处。如图1所示。 图1 1. 选择ccs的菜单Profiler中的enable clock,如图所示。 图2 2. 选择Profiler菜单下的 clock setup子菜单,并在Instruction Cycle中输入你的DSP时钟周期,它的单位为纳秒,例如,2407的系统时钟为40MHz,你就该填入 ..

[查看全文]

异步时钟数据同步方法

2013-02-05

11

关于gray code冗余的思考带来了一个全新方案,这个方案将为异步时钟间的数据传输 提供一个普遍的解决方案。 问题是:数据从一个时钟wr_clk,其件数据有效用valid 来指示,怎样将数据传递到另外的一个时钟rd_clk域?这里不对时钟频率做任何假设。 这个问题有以下这么几个关键点: 1. 异步输入亚稳态。 2. 无法用一个时钟采样一个宽度 ..

[查看全文]

allegro使二条时钟线等长

2013-02-02

无名小卒

19

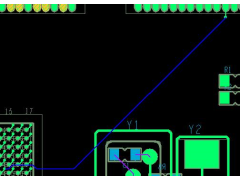

为了使二个SDRAM的时钟线等长,我查阅了很多资料,设置等长的方法有很多,在这里我们只为了二条时钟线等长来学习如何通过设置约束规则然后通过延时处理达到等长的目的。 首先是我们先要为想要等长的线找一个精确的数据,为此,我先布设了最长的那条时钟线 然后,通过display-->element查看他的长度,可以看到: Net path le ..

[查看全文]

FPGA异步时钟设计中的同步策略

2013-01-30

廖艳 王广君 高杨

5

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。本文总结出了几种同步 ..

[查看全文]

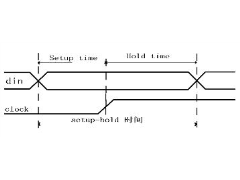

SPI总线时钟极性和时钟相位的概念理解

2013-01-29

26

SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。 其工作模式有两种:主模式和从 ..

[查看全文]

DSP 5402时钟与定时器中断FAQ

2013-01-28

33

时钟 VC5402的核电压为1。8V,从DATASHEET上了解到,外部时钟的电平不能超过1。8V,而一般的4脚有源晶振都是5V,请问高人有何解决办法? 1。一般四脚的卧室有源晶振在3。3V可以工作,还可以在输出脚串一100左右的电阻。 2.请用CMOS工艺的晶振(3。3V),市面上常见的晶振为TTL工艺(3。3V)和晶振厂家联系。 我的 ..

[查看全文]

推荐文章

最新文章

热门文章