关于gray code冗余的思考带来了一个全新方案,这个方案将为异步时钟间的数据传输

提供一个普遍的解决方案。

问题是:数据从一个时钟wr_clk,其件数据有效用valid

来指示,怎样将数据传递到另外的一个时钟rd_clk域?这里不对时钟频率做任何假设。

这个问题有以下这么几个关键点:

1. 异步输入亚稳态。

2. 无法用一个时钟采样一个宽度小于一个周期(包括等于,还需要考虑建立保持时间) 的信号。

3. 在将一组信号从一个时钟传递到另外一个时钟的时候,需要考虑各个信号通路上的延迟不同以及信号上的毛刺这两个问题。

4. 必须保证数据的不能够丢失。

5.

解决方案:

基本思想是首先将数据缓冲起来,然后挨个的读取数据。具体方法包括:

1。有一组缓冲区n个。n必须足够大,以便缓冲区不会溢出。

2。读写双方都维护一个指针,表示将要存取的缓冲区,这个指针在数据读写 之后将增加1,并循环。

3。写方通过gray code将信息传递到读的一方,其gray code每写一个数据增加1,读方维护自己的gray code,每次读取数据之后增加1,并比较自己的gray code和写方的gray code ,如不相等,表示可以进行一次读取。

并反复进行下去。

讨论 :

1. 需要多少个缓冲区?这需要由数据有效频率和读取速度和延迟来确定。一般的答案依赖于wr_clk的频率,rd_clk的频率,valid的模式,为了消除亚稳态和其他附加的延迟。

2.为什么需要采用gray code ? 采用gray code是为了满足面的要求3。

3.gray code需要多少位? 一般的考虑上面的要求2。至少需要的位数将是保证gray code 每一位的宽度可满足要求2的最小值。

4.还有其他么? 如果gray code的个数小于了缓冲区的个数(一些情况下发生),可以简单的将gray code多一些位,来避免复杂的控制操作。

5.在wr_clk频率大于rd_clk得时候情况如何?这个电路可以很好的工作,并代替原来的将valid信号接入触发器时钟端和异步复位的办法,并具有更简单的静态时序。

6,还有其他么?如果这个方法属于原创的话,建议把它叫做 PPL方法,或者PPL电路。 PPL(皮皮鲁),是陪伴了我10年以上《童话大王》里的主人公。相信很多人都看过。

-

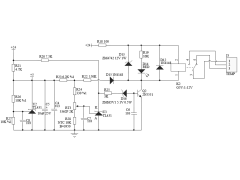

一款高温报警电路2024年11月13日 81

-

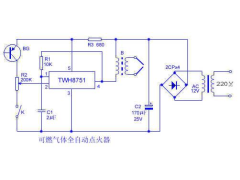

可燃气体全自动点火器2012年09月22日 76

-

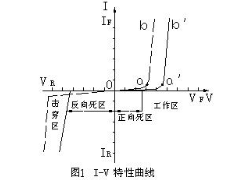

LED参数与特性2012年09月18日 118

-

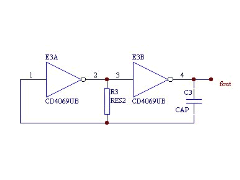

RC振荡电路的几种接法2012年09月10日 221

-

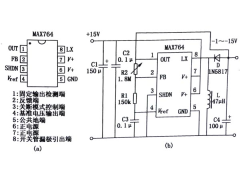

MAX764极性反转电路2012年08月24日 47

-

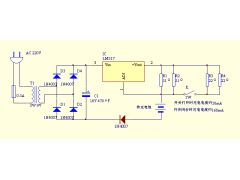

实用恒流充电器2012年08月18日 175

-

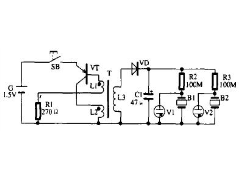

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4874

-

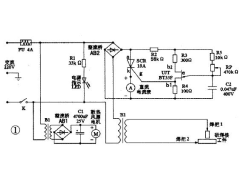

自制微型交流电焊机2012年07月14日 1143

-

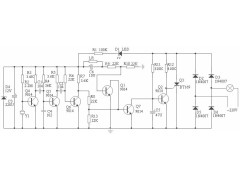

声光控延时开关的制作2024年07月06日 915

-

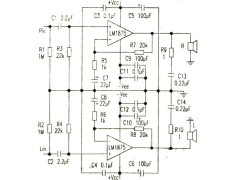

用LM1875替找TDA20302012年09月15日 777

-

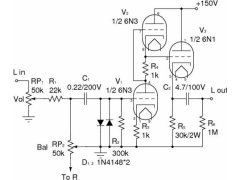

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

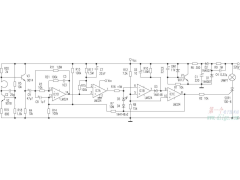

1000米晶体稳频FM立体声发射机2012年07月22日 499