NIOS II常用函数整理

2013-03-23

slam

16

IO操作函数 函数原型:IORD(BASE, REGNUM) 输入参数:BASE为寄存器的基地址,REGNUM为寄存器的偏移量 函数说明:从基地址为BASE的设备中读取寄存器中偏移量为REGNUM的单元里面的值。寄存器的值在地址总线的范围之内。 返回值:- 函数原型:IOWR(BASE, REGNUM, DATA) 输入参数:BASE为寄存器的基地址,REGNUM ..

[查看全文]

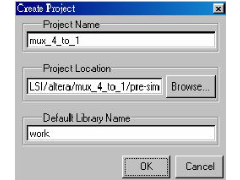

ModelSim+Synplify+Quartus的Altera FPGA的仿真与验证

2013-03-22

chenhongyi

52

作者:chenhongyi 软件要求:ModelSimSE、Synplify Pro、Quartus II 适用人群:初学者 源 代 码:mux4_to_1.v 工作内容: 1、设计一个多路选择器,利用ModelSimSE做功能仿真; 2、利用Synplify Pro进行综合,生成xxx.vqm文件; 3、利用Quartus II导入xxx.vqm进行自动布局布线,并生成xxx.vo(Verilog 4、利用ModelSimSE ..

[查看全文]

FPGA三国志-第四篇/工具篇

2013-03-19

wisdomz

10

FPGA的公司实际上换而言之,也可以成为EDA的公司了,只是他们在这方面的能力是否强大而已.这3家公司中,拥有自己HDL的公司只有Altera.可能很多人不太清楚,就是AHDL,当然这种语言的辉煌期已经过去了.这里说这个,绝对不是鼓励大家用这个语言. 这3家主要的开发软件大家都知道,在中国应该以Quartus II用的最广.ISE次之.但是现 ..

[查看全文]

介绍状态机的一种书写方式

2013-03-17

11

借用zqadam的逻辑改的: `define S1 0 `define S2 1 `define S3 2 `define S4 3 `define S5 4 `define S6 5 `define S7 6 `define S8 7 module clk_gen2 (clk,reset,clk1,clk2,clk4,fetch,alu_clk); input clk,reset; output clk1,clk2,clk4,fetch,alu_clk; wire clk,reset; reg clk2,clk4,fetch,alu_clk; reg[7:0] state,next_state ..

[查看全文]

Modelsim 初学者心得

2013-03-17

11

我刚刚接触modelsim,我想大多数菜鸟跟我一样,看过如何使用ModelSim的介绍,说句实话,那些介绍写的都太过简单,仿佛大家都不屑写上一些比较“弱智”的步骤,恰恰就是这些看似累赘的步骤,难为我好久。 教程上都写道,modelsim的简单使用方法如下:建立库- 影射库到物理目录 - 编译代码 - 启动仿真。首先建立库就 ..

[查看全文]

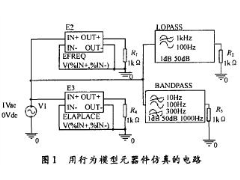

仿真软件Multisim与PSpice在电路设计中的功能比较

2013-03-16

庄小利 吴季

31

随着计算机技术的迅速发展,计算机辅助设计技术(CAD)已渗透到电子线路设计的各个领域,包括电路图生成、逻辑模拟、电路分析、优化设计、最坏情况分析、印刷板设计等。目前国际上比较流行两个仿真软件:Multisim (EWB的版本)和PSpice。通过对两个软件的认真学习和反复比较,发现二者存在很多差异,下面进行一一说明。 1 Mu ..

[查看全文]

Verilog学习笔记

2013-03-16

9

一般认为 Verilog HDL在系统级抽象方面比VHDL略差一些,而在门级开关电路描述方面比VHDL要强的多 写了第一个verilog程序,是一个加法器内容如下 module adder(count,sum,a,b,cin); input[2:0] a,b; input cin; output count; output [2:0] sum; assign{count,sum}=a+b+cin; endmodule 开始编译出现了几次错误,后来发现给实体 ..

[查看全文]

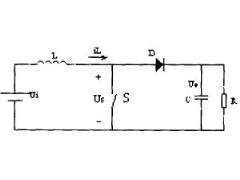

BOOST 电路的PSpice仿真分析

2013-03-16

韩彬 景占荣 高田

13

摘要:BOOST(升压型)电路的工作过程包括电路启动时的瞬态工作过程和电路稳定后的稳态工作过程。PSpice是一款功能强大的电路仿真软件,可对各种模拟和数字电路进行仿真,仿真结果十分接近电路的真实状态。本文应用PSpice对BOOST 电路的全部工作过程进行了仿真,对电路中储能元件的各种工作状态进行了分析,并从能量传递角 ..

[查看全文]

FPGA的一些设计方法

2013-03-15

13

1FPGA设计中的同步设计 在FPGA的内部资源里最重要的一部分就是其时钟资源(全局时钟网络),它一般是经过FPGA的特定全局时钟管脚进入FPGA内部,后经过全局时钟BUF适配到全局时钟网络的,这样的时钟网络可以保证相同的时钟沿到达芯片内部每一个触发器的延迟时间差异是可以忽略不计的。 在FPGA中上述的全局时钟网络被称为 ..

[查看全文]

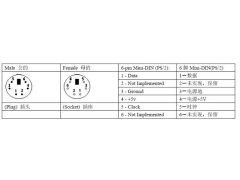

Verilog模拟PS2协议

2013-03-14

13

本来以为模拟PS2协议相当的麻烦,今天下了一本PS2协议手册看了半天,原来读键盘值相当简单嘛,比模拟SPI、I2C简单多了呵呵。 下面介绍一下具体过程 1.明确接线关系,只需接4根线,VCC要+5V,3.3我测试过不能用,时钟和数据线要用bidir双向口线,FPGA可以不用外接上拉电阻。另外,USB键盘也可以用,只要用一个转接头转成 ..

[查看全文]

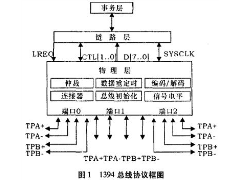

从1394 VHDL代码移植看FPGA设计

2013-03-12

汪国有 龙翔林

14

1 引言 IEEE1394是在计算机与外设直接进行高速数据传输的串行总线,因其具有传输速度高、支持即插即用、支持多达63个设备级联、以及设备间传输无需主机干预等特点,以至从其一出现就备受青睐。因IEEE 1394协议中的物理层可以在链路层不激活的情况下,作为中间节点而存在于1394网络中,物理层具有单独存在的意义,因此应用 ..

[查看全文]

一个好用的Verilog串口UART程序

2013-03-12

17

出自http://www.asic-world.com/,测试过了很好用。==========================================================================//----------------------------------------------------- // Design Name : uart // File Name: uart.v // Function: Simple UART // Coder: Deepak Kumar Tala //------- ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310