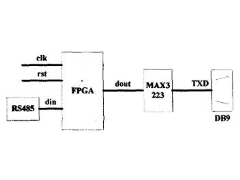

Verilog串口通讯设计

2013-03-11

11

1 串口通信基本特点 随着多微机系统的应用和微机网络的发展,通信功能越来越显得重要。串行通信是在一根传输线上一位一位地传送信息.这根线既作数据线又作联络线。串行通信作为一种主要的通信方式,由于所用的传输线少,并且可以借助现存的电话网进行信息传送,因此特别适合于远距离传送。在串行传输中,通信双方都按通信协议 ..

[查看全文]

八位的伪随机数产生的verilog源程序

2013-03-11

11

linear-feedback-shift-register 下面是一个八位的伪随机数产生的verilog文件,我想够用了。 // DEFINES `timescale 1ns/1ns `define DEL1// Clock-to-output delay. Zero // time delays can be confusing // and sometimes cause problems. // These are good tap values for 2 to 32 bits `define TAP22'b11 `define TAP33' ..

[查看全文]

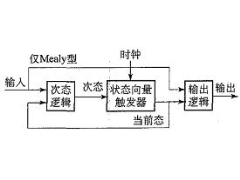

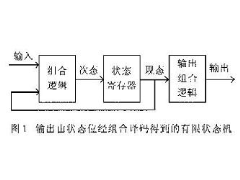

消除状态机毛刺策略探讨

2013-03-11

鲁玲 刘大年

14

随着EDA技术的高速发展,以大规模和超大规模器件FPGA/CPLD 为载体、以VHDL(硬件描述语言)为工具的电子系统设计越来越广泛。有限状态机(简称状态机)作为数字系统控制单元的重要设计方案之一,无论与基于VHDL语言的其他设计方案相比,还是与可完成相似功能的CPU设计方案相比,在运行速度的高效、执行时间的确定性和高可 ..

[查看全文]

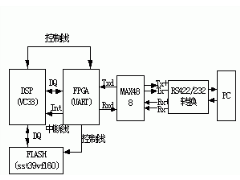

用FPGA实现DSP远程在线编程

2013-03-11

15

摘要:本文介绍了一种新的使用串行通信进行DSP远程在线编程方法。对设计中的主要技术:DSP与PC机的串口通信、Flash编程以及DSP自引导等进行了详细介绍。结合TI公司的TMS320VC33处理器,阐述了具体的实现方法。 关键词:DSPFPGA串口FLASH 随着微电子技术的飞速发展,通用数字信号处理器(DSP)的性价比不断提高,在数 ..

[查看全文]

基于RTL综合策略的状态机优化方法

2013-03-10

石松华 任浩琪

21

有限状态机及其设计技术是数字系统设计中的重要组成部分,是实现高效率、高可靠性逻辑控制的重要途径。大部分数字系统都可以划分为控制单元和数据单元两个组成部分。通常,控制单元的主体是一个状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。状态机性能的好坏对系统性能有较大的影响。良好的状态机的实 ..

[查看全文]

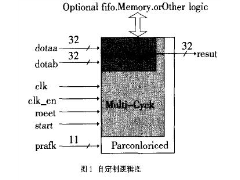

自定制Nios处理器的FFT算法指令

2013-03-10

管立新

11

1 引言 在Altera的Nios嵌入式处理器中。用户可以在Nios指令系统中增加用户自定制指令来满足某种特定的应用需求。自定制指令可以访问存储器或Nios系统外的逻辑资源。增强系统的实时处理能力,特别适用于DSP、数据包处理及对计算密集型软件进行优化。 Altera高性能快速傅立叶变换(FFT)处理器IP核FFT V2.2.0为实现高速FFT算法 ..

[查看全文]

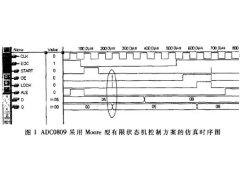

VHDL设计MOORE型有限状态机时速度问题的探讨

2013-03-10

朱小莉 陈迪平 王镇道

22

1 引言 随着微电子技术的迅速发展,人们对数字系统的需求也在提高。不仅要有完善的功能,而且对速度也提出了很高的要求。对于大部分数字系统,都可以划分为控制单元和数据单元两个组成部分。通常,控制单元的主体是一个有限状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。MOORE型有限状态机的设计方 ..

[查看全文]

带进位加法器之VHDL描述

2013-03-09

skycanny

22

学过VHDL的人都知道,VHDL是提供了操作符“+”,而且在很多情况下,我们是可以直接用这个加操作符的。但是,VHDL提供的加法操作只能给出 “和”,却无法给出“进位”。例如我们在设计计数器的时候经常用到的加1操作,对于一个8位的计数器,当计数器的结果为0xff时,如果在加1就为 0x0 ..

[查看全文]

Verilog-HDL的基本概念

2013-03-09

常晓明

13

Verilog-HDL与CPLD/FPGA设计应用讲座 第 3 讲 Verilog-HDL的基本概念 3.1 与门的描述 3.2 与非门的描述 3.3 非门的描述 3.4 或门的描述 3.5 或非门的描述 3.6 缓冲器的描述 3.7 逻辑仿真与测试模块 3.1 与门的描述 让我们通过最简单的例子来认识一下Verilog-HDL的基本用法。 (1)模块的定义 用Verilog-HDL做数字电路描述,一开始所 ..

[查看全文]

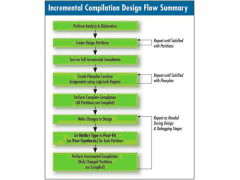

采用编译增强技术,提高高密度FPGA设计工作效率

2013-03-07

19

现场可编程门阵列(FPGA)体系创新以及向90nm工艺技术的过渡显著提高了FPGA的密度和性能。FPGA设计人员不仅需要更高的逻辑密度和更快的性能表现,还要求具有嵌入式处理器、数字信号处理(DSP)模块以及其他硬件IP结构等复杂的器件功能。但是,由于FPGA设计规模越来越大、越来越复杂,为了能够抓住稍纵即逝的市场机会, ..

[查看全文]

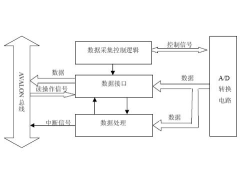

在NIOS-II 系统中A/D数据采集接口的设计与实现

2013-03-05

唐重陈 周锋 黄自瑞

16

随着电子技术的发展,电子系统设计的规模和复杂程度不断的加大,与此同时,人们对电子产品的各方面性能的要求都在不断的升高,对于开发商来说,以最快的速度,开发出满足市场需要的电子产品是最根本的目的。显然,传统的硬件、软件单独设计的方式很难满足人们这种快速增长的需求。近年来,电子行业提出了软硬件协同起来进行 ..

[查看全文]

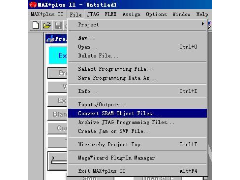

用CPU配置FPGA(三)软件操作

2013-03-05

11

编程文件格式的转换 MAX+plusII或QuartusII生成的SOF或POF文件不能直接用于CPU配置FPGA中,需要进行数据转换才能得到软件可用的配置数据。在MaxplusII中的具体步骤如下: 1. 进入数据转换对话框 图1 进入数据转换对话框 2.选择需要转换的SOF文件,对于配置多个FPGA的场合,应选择所有的SOF文件并排好次序。输出文件的格 ..

[查看全文]

推荐文章

-

热敏电阻温度阻值查询程序2024年11月13日 109

-

C99语法规则2024年11月16日 1004

-

FreeRTOS 动态内存管理2024年11月12日 484

-

一款常用buffer程序2024年11月06日 121

-

1602液晶显示模块的应用2012年08月03日 203

-

GNU C 9条扩展语法2024年11月18日 299

最新文章

-

Corext-M3中断的具体行为2025年11月11日 66

-

优秀的字符串哈希算法-ELFhash2024年11月26日 110

-

SD卡TF卡引脚定义2024年11月26日 105

-

C语言string.h常用函数重点说明2024年11月22日 62

-

C语言下划线命名法2024年11月22日 73

-

C数组 结构体 联合体快速初始化2024年11月22日 60

热门文章

-

C99语法规则2024年11月16日 1004

-

51单片机LED16*16点阵滚动显示2012年09月05日 671

-

FreeRTOS 动态内存管理2024年11月12日 484

-

ARM9远程图像无线监控系统2012年07月03日 435

-

用单片机模拟2272软件解码2012年09月06日 311

-

如何实现STM32F407单片机的ADC转换2024年11月15日 310