作者:chenhongyi

软件要求:ModelSimSE、Synplify Pro、Quartus II

适用人群:初学者

源 代 码:mux4_to_1.v

工作内容:

1、设计一个多路选择器,利用ModelSimSE做功能仿真;

2、利用Synplify Pro进行综合,生成xxx.vqm文件;

3、利用Quartus II导入xxx.vqm进行自动布局布线,并生成xxx.vo(Verilog

4、利用ModelSimSE做后仿真,看是否满足要求。

注:

1. 仿真器(Simulator)是用来仿真电路的波形。

2. 综合工具(Synthesizer)的功能是将HDL转换成由电路所组成的Netlist。

3. 一般而言,在电路设计的仿真上可分为Pre-Sim 和Post-Sim。Pre-Sim 是针而Post-Sim则是针对综合过且做完成了Auto Place and Route(APR)的电路进行仿真,以确保所设计的电路实现在FPGA上时,与Pre-Sim 的功能一样。

1、前仿真(Pre-Sim)

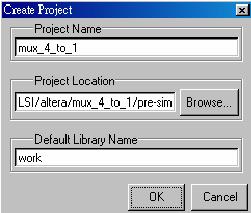

步骤一:打开ModelSimSE,然后建立一个Project;

※建立Project的方式为点选File → New → Project…;

※设定Project Name 与Project location,按OK 即可建立Project。

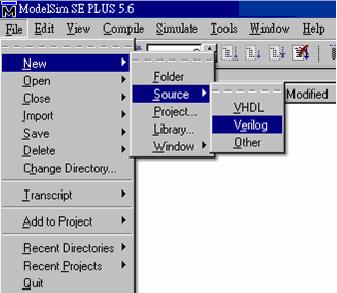

步骤二:新增设计文档或加入文档。

※新增文档的方式为点选File → New → Source → Verilog,然后对文档进行编辑并储存为xxx.v;

※ 加入文档的方式为点选File → Add to Project → File...,然后点选xxx.v;

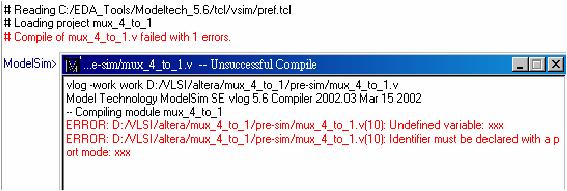

步骤三:编译(Compile)。

※编译文档的方式为点选Compile → Compile All,即可编译所有的文档。

※如果编译时发生错误,在显示错误的地方(红字)点两下,即可跳到错误。

步骤四:新增或加入测试平台(Testbench)。

※当设计完电路后,为了确定所设计的电路是否符合要求,我们会写一个测 试平台(Testbench);

※ 新增或加入测试平台,然后编译它。

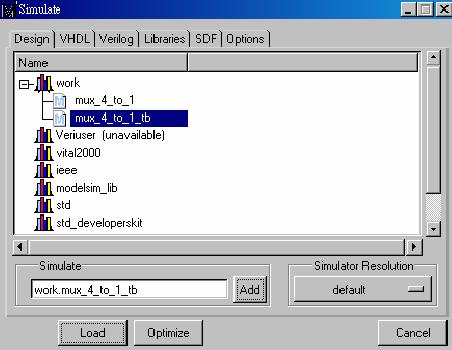

步骤五:仿真(Simulate)。

※仿真的方式为点选Simulate → Simulate…;

※打开Design里面的work,然后点选mux_4_to_1_tb 并Add 它,最后按Load 即可跳到仿真窗口。

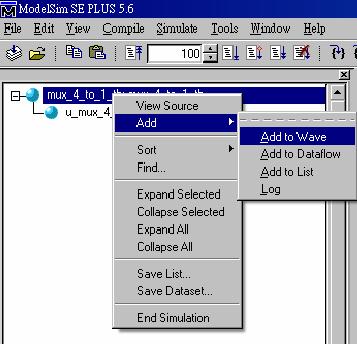

步骤六:加入信号线。

※ 在窗口上按右键,然后点选Add → Add to Wave;

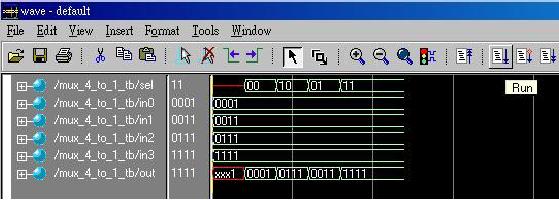

步骤七:看波形。

※在工具列上按Run,然后就会显示波形;

※慢慢看波形吧,没有波形就没有真相!

以上就是使用ModelSim做Pre-Sim的基本流程,在此要特别强调的是,ModelSim所有的功能并不仅仅于此,如果你想要了解更多的话,一切都要靠自己花时间去问去试,只有努力的人才能有丰富的收获,加油!

-

热敏电阻温度阻值查询程序2024年11月13日 74

-

C99语法规则2024年11月16日 675

-

FreeRTOS 动态内存管理2024年11月12日 448

-

一款常用buffer程序2024年11月06日 88

-

1602液晶显示模块的应用2012年08月03日 192

-

GNU C 9条扩展语法2024年11月18日 261

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

STM32使用中断屏蔽寄存器BASEPRI保护临界段2024年11月15日 195

-

C99语法规则2024年11月16日 675

-

51单片机LED16*16点阵滚动显示2012年09月05日 664

-

FreeRTOS 动态内存管理2024年11月12日 448

-

ARM9远程图像无线监控系统2012年07月03日 424

-

用单片机模拟2272软件解码2012年09月06日 300

-

如何实现STM32F407单片机的ADC转换2024年11月15日 300

-

新颖的单片机LED钟2012年08月06日 278

-

GNU C 9条扩展语法2024年11月18日 261