日常生活中,我们常常可以看到这样的现象,当把手机放置在音箱旁,接电话的时候,音箱里面会发出吱吱的声音,或者当我们在测试一块电路板上的波形时,忽然接到同事的电话,会发现接电话瞬间我们示波器上的波形出现变形,这些都是电磁干扰的特征。电磁干扰不但会影响系统的正常工作,还可能给电子电器造成损坏,甚至对人体也有害处,因此尽可能降低电磁干扰已经成为大家关注的一个焦点,诸如FCC、CISPR、VCCI等电磁兼容标准的出台开始给电子产品的设计提出了更高的要求。虽然人们对电磁兼容性的研究要远远早于信号完整性理论的提出,但作为高速设计一部分,我们习惯地将EMI问题也列入信号完整性分析的一部分。本章将全面分析电磁干扰和电磁兼容的概念、产生及抑制,重点针对高速PCB的设计。

4.1 EMI/EMC的基本概念

电磁干扰即EMI(Electromagnetic Interference),指系统通过传导或者辐射,发射电磁波并影响其他系统或本系统内其他子系统的正常工作。因为所有的电子产品都会不可避免地产生一定的电磁干扰,为了量度设备系统在电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁干扰的能力,人们提出了电磁兼容这个概念。美国联邦通讯委员会在1990年和欧盟在1992都提出了对商业数码产品的有关规章,这些规章要求各个公司确保它们的产品符合严格的磁化系数和发射准则。符合这些规章的产品称为具有电磁兼容性EMC(Electromagnetic Compatibility)。对于电磁兼容性,必须满足一下三个要素:

- 电磁兼容需要存在某一个特定的空间。比如,大的,一个房间甚至宇宙;小的,可以是一块集成电路板。

- 电磁兼容必须同时存在骚扰的发射体和感受体。

- 必须存在一定的媒体(耦合途径)将发射体与感受体结合到一起。这个媒体可以是空间,也可以是公共电网或者公共阻抗。

对于EMI,可以按照电磁干扰的途径(详细的分类参见附录一)来分为辐射干扰、传导干扰和感应耦合干扰三种形式。辐射干扰就是指如果骚扰源不是处在一个全封闭的金属外壳内,它就可以通过空间向外辐射电磁波,其辐射场强取决于装置的骚扰电流强度、装置的等效阻抗,以及骚扰源的发射频率。如果骚扰源的金属外壳带有缝隙与孔洞,则辐射的强度与干扰信号的波长有关。当如果孔洞的大小和波长可以比拟时,则可形成干扰子辐射源向四周辐射,辐射场中金属物还可以形成二次辐射;传导干扰,顾名思义,骚扰源主要是利用与其相连的导线向外部发射,也可以通过公共阻抗耦合,或接地回路耦合,将干扰带入其他电路,传导干扰是电磁干扰的一种重要形式;感应耦合干扰的途径是介于辐射途径与传导途径之间的第三条途径,当骚扰源的频率较低时,骚扰电源的辐射能力有限。同时骚扰又不直接与其他导体连接,此时电磁骚扰能量则通过与其相邻的导体产生感应耦合,将电磁能转移到其他导体上去,在邻近导体内感应出骚扰电流或者电压。感应耦合可以通过导体间的电容耦合的形式出现,也可以由电感耦合的形式或电容、电感混合出现。

4.2 EMI的产生

我们来分析一下EMI的产生,忽略自然干扰的影响,在电子电路系统中我们主要考虑是电压瞬变和信号的回流这两方面。

4.2.1电压瞬变

对于电磁干扰的分析,可以从电磁能量外泄方面来考虑,如果器件向外泄露的能量越少,我们可以认为产生的电磁干扰就比较小。对于高速的数字器件来说,产生高频交流信号时的电压瞬变是产生电磁干扰的一个主要原因。我们知道,数字信号在开关输出时产生的频谱不是单一的,而是融合了很多高次谐波分量,这些谐波的振幅(即能量)由器件的上升或者下降时间来决定,信号上升和下降速率越快,即开关频率越高,则产生的能量越多。所以,如果器件在很短的时间内完成很大的电压瞬变,将会产生严重的电磁辐射,这个电磁能量的外泄就会造成电磁干扰问题。通常,高速数字电路的EMI发射带宽可以通过下面的公式计算:

F=1/πTr,

F为开关电路产生的最高EMI频率,单位为GHz,Tr为信号的上升时间或者下降时间,单位为ns。

比如,对于上升时间为1ns左右的器件,那么它所产生的最高EMI频率将为350MHz,而如果上升时间降为为500ps,那么它的最高EMI发射频率将为700MHz,远远高于系统正常的工作频率,这将会在一定程度上影响周围其他系统的正常工作。

显然,如果能减缓信号的上升沿,将会在很大程度上减少EMI,但是随着电子设计和芯片制造水平的发展,器件总是朝着高速方向发展,单一的降低信号开关速率显然是不现实的。但我们却可以通过降低信号电压来达到同样的目的,因为在相同的时间内,低电压器件需要跨越的逻辑门电压幅度较小,就同样减缓器件的上升沿速率,所以低电压器件也是高速电路发展的趋势。

4.2.2信号的回流

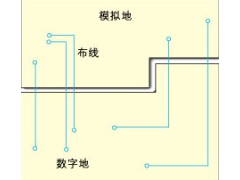

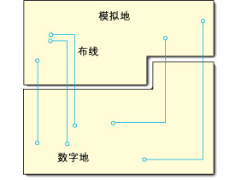

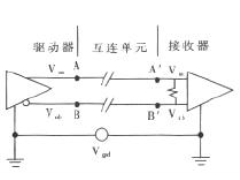

任何信号的传输都存在一个闭环的回路,当电流从驱动端流入接收端的时候,必然会有一个回流电流通过与之相邻的导体从接收端回流至驱动端,构成一个闭合的环路,而环路的大小却和EMI的产生有着很大的关系,我们都知道,每一个环路都可以等效为一个天线,环路数量或者面积越大,引起的EMI也越强。我们知道,交流信号会自动选取阻抗最小的路径返回驱动端,但实际情况中,信号不可能始终保持如图1-4-1-1所示的理想路径,特别是在高密度布线的PCB板上,过孔,缝隙等都可能降低参考平面理想的特性,而是表现为更复杂的回流形式(图1-4-2)。

图1-4-1 理想信号回流示意图

图1-4-1 实际情况中的信号回流

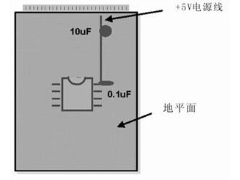

对高频信号回流的理解不能有一个思维定势,认为回流必须完全存在于信号走线正下方的参考平面上。事实上,信号回流的途径是多方面的:参考平面,相邻的走线,介质,甚至空气都可能成为它选择的通道,究竟哪个占主要地位归根结底看它们和信号走线的耦合程度,耦合最强的将为信号提供最主要的回流途径。比如在多层PCB设计中,参考平面离信号层很近,耦合了绝大部分的电磁场,99%以上的信号能量将集中在最近的参考平面回流,由于信号和地回流之间的环路面积很小,所以产生的EMI也很低。但如果由于相邻的参考平面上存在缝隙等非理想因素,这就导致了回流的面积增大,低电感的耦合作用减弱,将会有更多的回流通过其它途径或者直接释放到空中,这就会导致EMI的大大增加。

我们参考图1-4-3来分析信号回流对EMI的影响,可以看到:信号和回流外部区域,由于磁场的极性相反,可以相互抵消,而中间部分是加强的,这也是对外辐射的主要来源。很明显,我们只要缩短信号和回流之间的距离,就可以更好的抵消外围的电磁场,同时也能降低中间加强部分的面积,大大抑制EMI。

图1-4-3信号回路的磁场耦台分析

4.2.3 共模和差摸EMI

当两条或者多条信号线以相同的相位和方向从驱动端输出到接收端的时候,就会产生共模干扰。共模特性表现为这些导线组中的感生电流方向全部相同,而产生的磁场也是他们相同方向磁场的迭加,增大了磁场强度,向外辐射能量的大天线就是这样形成的。在共模的情况下,会导致磁场强度的变大和电场强度减小,这样就相当于增加了传输线的电感和减小传输线的电容值。因此,如果传输线的阻抗变大,电磁场能量外泄增加,电磁干扰也变大。

电源线上电流从驱动端流到接收端的时候和它回流之间耦合产生的干扰,就叫做差模干扰。电流流向负载时,会产生等值的回流,这两个方向相反的电流,当回流电流完全居于传输电流下方的时候,就形成了标准的差模信号。由于它们相互之间产生的磁场方向相反,因而可以抵消大部分的磁场,抑制了磁场的外泄比率,而其中残留的电磁场就形成了差模EMI。

通常,线路上这两种电磁干扰是同时存在的,由于线路的阻抗不平衡,两种分量在传输过程中回相互转变,情况十分复杂。干扰在线路上经过长距离传输后,由于线路阻抗和地线阻抗不同,差模干扰的衰减要比共模干扰的衰减大,因此控制共模干扰往往比控制差模干扰要困难的多。

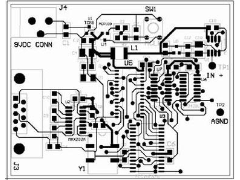

在PCB的电磁兼容设计中,主要考虑的标准是电路板对外辐射能量的多少,所有的辐射分为共模辐射和差模辐射两种。PCB上的每根信号走线都会引起一定的共模辐射,在传输线阻抗很高、终端开路的情况下引起的共模辐射最强,也可以从单根天线的角度考虑。而由信号走线和回流之间的回路引起的辐射称为差模辐射,可以看为简单的环形天线。一般来说,共模辐射的影响要更为严重,所以在高速PCB抑制EMI的设计中,有一个很重要的思想就是“将共模辐射转化为差模辐射”。这是如何实现的呢?刚才说到,造成强烈的共模辐射的条件就是高阻抗走线和高阻抗的负载(开路),如果我们能有效地降低走线的阻抗,即缩小信号走线到参考平面的距离,就可以大大减小共模辐射的强度。此外,对终端进行合理的匹配,也可以降低高阻抗负载的影响。这时,对外电磁能量辐射的主体就转变为信号和回流之间的差模辐射。所以,我们在高速PCB的EMC设计中,往往更多地考虑电流回路,这并不是忽略共模辐射,而是在将共模辐射有效地转化为差模辐射的前提下,对EMI的整体控制。

-

怎样设计一块好的PCB板2012年07月28日 59

-

高速PCB设计指南(三)2013年03月27日 140

-

PCB布线设计(二)2013年03月23日 38

-

混合信号PCB的分区设计2013年03月04日 23

-

高速PCB设计指南(六)2012年12月29日 25

-

PCB布线设计(一)2012年10月22日 13

-

高速PCB设计指南(五)2012年10月15日 15

-

电气安全距离要求及分类2012年09月06日 273

-

PROTEL 99SE的打印设置2013年02月08日 381

-

Protel dxp等长走线2013年01月02日 329

-

Cadence 中添加工艺库文件步骤2013年01月16日 280

-

电气安全距离要求及分类2012年09月06日 273

-

在ORCAD中整体修改网络名称2012年07月26日 173

-

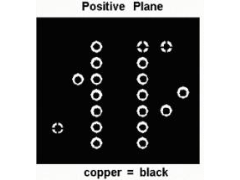

Allegro铺铜的学习2012年12月05日 171

-

Altium Designer焊盘为梅花状连接,过孔为直接连接的方法2013年01月25日 159

-

差分信号线的分析和LAYOUT2012年09月16日 144