原文作者:Mujtaba Hamid

注:

一个设计的测试验证是非常重要的。有效的测试可以助我们快速的完成或改善设计。Testbenches建议编写有效的测试代码来通过软件实现可靠的验证。无意中发现,顺手译为中文,以备将来方便。也贴给没有找到更好中文版本的同道人。

Testbenches本意应该是测试平台更合理,但是在中文中阅读起来很不舒服。所以本文中有时译为“测试设计”,“测试代码”,有时干脆是“测试”。摘要:

应用笔记为HDL验证设计的新手,或者是没有丰富的测试设计经验的逻辑设计者而编写。

测试设计是验证HDL设计的主要手段。本应用笔记为创建或准备和构建有效的测试设计提供准则。它也提供一个为任何设计开发自较验测的测试设计的一个代数方法。

涉及的所有设计文件可以从以下的站点获得:

PC: ftp://ftp.xilinx.com/pub/applications/xapp/xapp199.zip

UNIX: ftp://ftp.xilinx.com/pub/applications/xapp/xapp199.tar.gz简介:

由于设计的规模越来越大和越来越复杂,数字设计的验证已经成为一个日益困难和繁琐的事。面对挑战,验证工程师们依靠许多的验证工具和方法。对于大的系统,如几百万门的设计,工程师们一般使用一套可靠的验证工具。当然,对于一些小的设计,设计工程师常常发现带有测试的hdl仿真器就可以做得很好。

测试设计已经成为一个验证高级语言设计HLL (High-Level Language) 的标准方法。

典型的,测试设计完成以下任务:

实现测试设计;

仿真通过使用模块的测试向量来仿真测试设计;

输出结果到终端或波形窗口以检视;

可选择的将实际结果和预期结果进行比较。

一般测试设计使用工业标准的VHDL或verilog硬件描述语言来编写。测试设计调用功能设计,然后仿真。复杂的测试设计完成一些附加的功能----如它们包含逻辑来为设计决定适当的设计激励或比较实际结果和预期结果。

后续的章节说明了一个非常稳定的测试设计的结构,并且提供了一个自较验测例子----它将自动比较实际结果和测试设计的预期结果。

图1说明一个基于以上基本要求的标准的hdl验证流程。由于测试设计使用VHDL或verilogHDL来描述,测试设计的验证过程可以在不同的平台或不同公司的软件工具环境完成。另外,由于VHDL或verilogHDL是公开的通用标准语言,使用VHDL或verilogHDL来描述验证设计可以毫无困难的在将来重用。

图1使用测试设计的HDL测试验证流程构建测试设计:

测试设计可以用VHDL或verilogHDL来描述.因为测试设计只用来进行仿真,它们没有那些适应综合中仅应用的rtl语言子集的语法约束的限制.而是所有的行为结构都可以使用。从而测试设计可以编写的更为通用,使得它们可以更容易维护。

所有的测试设计包含了如表1的基本程序段块。正如上面所提到的,测试设计一般包含更多的附加功能,如在终端上可视的结果和内建的错误检测。

1 测试设计的基本程序段

下面的例子说明经常使用的测试设计的结构。产生时钟信号

使用系统时钟来的时序逻辑设计必须产生时钟。重复的时钟信号可以很容易的在vhdl或verilog源码中实现。以下是vhdl和verilog的时钟发生示例。

VHDL:

-- Declare a clock period constant.

Constant ClockPeriod : TIME := 10 ns;

-- Clock Generation method 1:

Clock <= not Clock after ClockPeriod / 2;

-- Clock Generation method 2:

GENERATE CLOCK: process

begin

wait for (ClockPeriod / 2)

Clock <= ’1’;

wait for (ClockPeriod / 2)

Clock <= ’0’;

end process;

Verilog:

// Declare a clock period constant.

Parameter ClockPeriod = 10;

// Clock Generation method 1:

initial begin

forever Clock = #(ClockPeriod / 2) ~ Clock;

end

// Clock Generation method 2:

initial begin

always #(ClockPeriod / 2) Clock = ~Clock;

end准备激励信号

为了获得测试设计的验证结果,激励必须在测试设计中提供。在测试设计中使用的并行激励块提供必要的激励。两个方法被考虑:绝对时间激励和相对时间激励。在第一个方法里,仿真变量被详细描述为相对于仿真时间零点。通过比较,相对时间激励提供初始值,然后在重触发激励前等待一个事件。根据设计者的需要,两种方法可以在测试设计中组合使用。

表2绝对时间激励

表2和表3分别以vhdl和verilog提供了一个绝对时间激励和相对时间激励的源代码。

表3相对时间激励

VHDL进程块和Verilog初始块与设计文件中的其他的进程块或初始块同时执行。然而,在每一个进程块或初始块中,事件是按照书写的顺序有序的规划的。这说明在仿真时间零点并发的每一个块激励的顺序。多模块应该被用来将复杂的激励顺序分解为有更好的可读性和方便维护的代码。 显示结果

在verilog中推荐使用关键字$display 和 $monitor 显示结果。虽然vhdl没有等效的显示指令,它提供了std_textio标准文本输入输出程序包。它允许文件的i/o重定向到显示终端窗口(作为这个技术的示例,参看下面的自较验查验证设计)

下面是verilog示例,它将在终端屏幕上显示一些值。

// pipes the ASCII results to the terminal or text editor

initial begin

$timeformat(-9,1,"ns",12);

$display(" Time Clk Rst Ld SftRg Data Sel");

$monitor("%t %b %b %b %b %b %b", $realtime,

clock, reset, load, shiftreg, data, sel);

end

关键字 $display在终端屏幕上输出引用的附加的说明文字(“。。。”).关键字$monitor操作不同。因为它的输出是事件驱动的。例中的变量$realtime(由用户赋值到当前的仿真时间)用于触发信号列表中值的显示。信号表由变量 $realtime开始,跟随其他将要显示的信号名(clock, reset, load等)。以%开始的关键字包含一个格式描述的表,用来控制如何格式化显示信号列表中的每个信号的值。格式列表是位置确定的。每个格式说明有序地与信号列表中的信号顺序相关。比如%t说明规定了$realtime的值是时间格式。并且第一个%b说明符格式化clock的值是二进制形式。verilog提供附加的格式说明,比如%h用于说明十六进制,%d说明十进制,%c说明显示为八进制。(参见verilog准则了解完整的关键字及格式描述符)

简单的测试设计

简单的测试设计实例化用户设计,然后提供相应的激励。测试输出被图形化显示在仿真器的波形窗口里或者作为文本发送到用户的终端或者是管道输出文本。

以下是一个简单的用Verilog实现的设计,它实现了一个移位寄存器的功能。

module shift_reg (clock, reset, load, sel, data, shiftreg);

input clock;

input reset;

input load;

input [1:0] sel;

input [4:0] data;

output [4:0] shiftreg;

reg [4:0] shiftreg;

always @ (posedge clock)

begin

if (reset)

shiftreg = 0;

else if (load)

shiftreg = data;

else

case (sel)

2’b00 : shiftreg = shiftreg;

2’b01 : shiftreg = shiftreg << 1;

2’b10 : shiftreg = shiftreg >> 1;

default : shiftreg = shiftreg;

endcase

end

endmodule

以下是简单的测试设计示例移位寄存器设计的例子,verilog描述。

module testbench; // declare testbench name

reg clock;

reg load;

reg reset; // declaration of signals

wire [4:0] shiftreg;

reg [4:0] data;

reg [1:0] sel;

// instantiation of the shift_reg design below

shift_reg dut(.clock (clock),

.load (load),

.reset (reset),

.shiftreg (shiftreg),

.data (data),

.sel (sel));

//this process block sets up the free running clock

initial begin

clock = 0;

forever #50 clock = ~clock;

end

initial begin// this process block specifies the stimulus.

reset = 1;

data = 5’b00000;

load = 0;

sel = 2’b00;

#200

reset = 0;

load = 1;

#200

data = 5’b00001;

#100

sel = 2’b01;

load = 0;

#200

sel = 2’b10;

#1000 $stop;

end

initial begin// this process block pipes the ASCII results to the

//terminal or text editor

$timeformat(-9,1,"ns",12);

$display(" Time Clk Rst Ld SftRg Data Sel");

$monitor("%t %b %b %b %b %b %b", $realtime,

clock, reset, load, shiftreg, data, sel);

end

endmodule

以上的测试设计实例化设计,设置时钟,提供激励信号。所有的进程块在仿真时间零点开始。英镑标记(#)说明下一个激励作用前的延迟。$stop命令使仿真器停止测试仿真(所有测试设计中都应该包含一个停止命令)。最后,$monitor语句返回ascII格式的结果到屏幕或者管道输出到一个文本编辑器。接后的是一个vhdl描述的的测试设计,它实例化设计并提供激励到上述用verilog描述的移位寄存器.

-

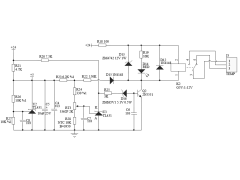

一款高温报警电路2024年11月13日 81

-

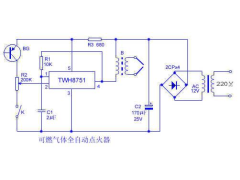

可燃气体全自动点火器2012年09月22日 76

-

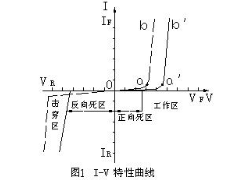

LED参数与特性2012年09月18日 118

-

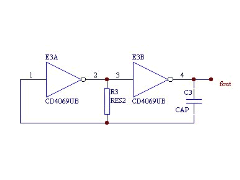

RC振荡电路的几种接法2012年09月10日 221

-

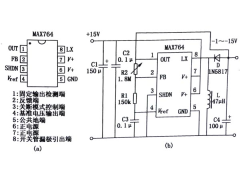

MAX764极性反转电路2012年08月24日 47

-

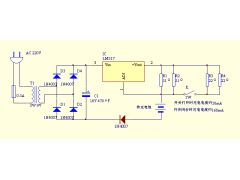

实用恒流充电器2012年08月18日 175

-

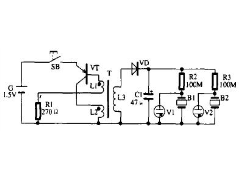

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4875

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

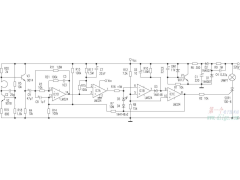

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499