设计实例

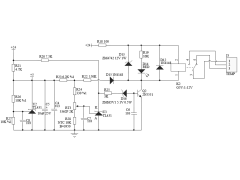

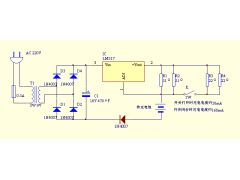

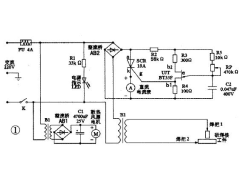

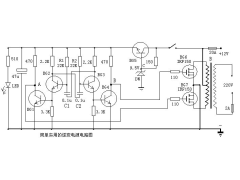

接着以Flyback type电源供应器(S.P.S: Switching Power Supply)为例,具体说明高功率电路pattern的layout技巧。Flyback type的电源供应器switching FET ON时,会将能量(energy)储存于变压器内(transformer),FET OFF时则将能量释放至OUTPUT端。表3与图5分别是Flyback type电源供应器的概要规格与电路图。

|

ITEN |

SPEC |

|

输入电压 |

AC95V~130V,50Hz/60Hz |

|

Switching频率 |

40KHz |

|

输出电压 |

+5V±5%,最大4A |

|

输出电流 |

±12V±3%,最大0.3A |

Flyback type电源供应器的概要规格

图5 Flyback type电源供应器的电路图

电源输入端(以下通称为1次端)与输出端(以下通称为2次端) 利用高频变压器(transf ormer) 绝缘,所以1次端与2次端的组件以 作区隔分离。本电路的输出电压不作复归,为获得IC的电源因此使补助卷线电压复归,所以整体而言能够轻易作1次端与2次端的隔离。此外如果基板的端缘很靠近筐体时,1次端的pattern与组件必需从基板端缘配置。图6是合成pattern图,图7与图8分别是组件面的pattern图与焊接面的pattern图。由于本设计例主要目的是以说明为主,所以并不代表电路动作与性能完美无瑕疵。

图6 switching电源供应器电路板的合成pattern

图7 switching电源供应器电路板的组件面pattern

图8 switching电源供应器电路板的焊接面pattern

有关Power电路单元

1次端pattern的设计要领

由于从C7+端子到T1 脚架1(pin 1)、从T1的脚架3(pin 3)到Q1 脚架1(pin 1),从Q1脚架(pin 3)通过R10,与另一C7 端子连接的pattern流有大电流,因此pattern必需设计成粗短状,同时尽量减少围绕面积,其结果如图9所示。

图9 Power电路板的1次端pattern

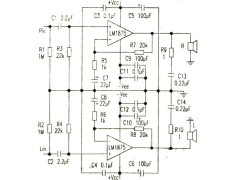

2次端pattern的设计要领

2次端pattern的设计与上述1次端一样,pattern必需设计成粗短状,同时尽量减少围绕面积,其结果如图10所示。

图10 Power电路板的2次端pattern

也就是说下列pattern必需与1次端一样,pattern必需设计成粗短:

- T1的脚架13(pin 13)以及从脚架14(pin 14)通过D10,再与C8以及C9的+端子连接的pattern。

- 从C8以及C9的-端子与T1的脚架11(pin 11)、脚架12(pin 12)连接的pattern。

电容并列连接时,需作等长配线设计

C8以及C9的连接如图4(b)所示,从T1观之+端子与-端子的合计pattern作等长连接,图10是C8以及C9部分pattern,外观上看似单纯的better pattern,不过如果仔细观察时事实上pattern却如图4(b)所示。

相关电路尽量集中设置

由D8,R8,C12构成的电路,以及D9,R11,C5构成的电路统称为snubber电路,因此将T1的脚架1(pin 1)、脚架3(pin 3)以及Q1 的drain设于source附近。实际上电流侦测阻抗会流入Q1的source,因此将D9,R11与R10连接。

设法降低pattern的阻抗

由于+12V端 C13,C14的pattern电流很低,因此不需加宽pattern,不过pattern围绕的面积很小,基于降低pattern的电感(inductance)等考虑,所以将common的pattern加宽成如图10(b)的结构。

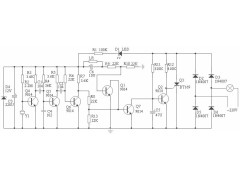

有关控制电路单元

将ground当作better pattern

如图11(b)所示控制电路单元的ground被当作better pattern与R10作1点连接。

图11 控制电路单元的pattern

控制IC周边的pattern

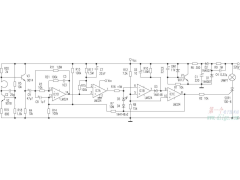

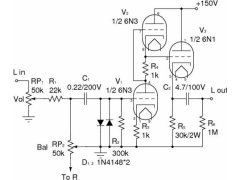

图12是UC3844A的方块图,由图可知C3是可以去除过电流检测电压噪讯的电容器,因此C3尽量设于U1脚架3附近。U1 的脚架2是电压复归输入端子,也是OP增幅器的加算点,所以从U1的脚架2延伸的pattern必需取最短距离。此外OP增幅器的加算点不可与其它pattern交叉。本电路的焊接面设有加算点pattern,同时刻意避免其它pattern通过组件面,具体方式如图11(a)所示,从U1的脚架8至R2的pattern绕过R4铺设。FET 的gate电阻R5则设于FET(Q1)附近,D2,D3可以保护 驱动输出电路不受电洞(surge)破坏的二极管因此设于U1 附近。

图12 UC3844A的方块图

结语

虽然类似Protel DXP等PCB-CAD设计软件祇需设定规则(rule),便可自动完成电路板的配线layout作业,不过事前的规划检讨与layout后的检查、修正作业,仍需仰赖长年累积的实务经验与基础素养,因此本文辅以实际设计实例,具体介绍有关高功率印刷电路板的设计技巧。

-

一款高温报警电路2024年11月13日 81

-

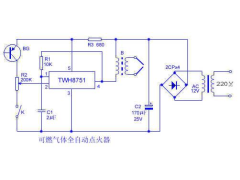

可燃气体全自动点火器2012年09月22日 76

-

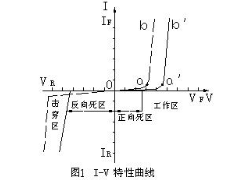

LED参数与特性2012年09月18日 118

-

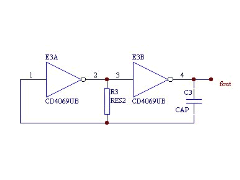

RC振荡电路的几种接法2012年09月10日 221

-

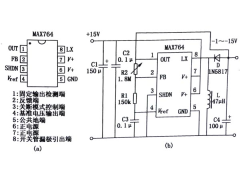

MAX764极性反转电路2012年08月24日 47

-

实用恒流充电器2012年08月18日 175

-

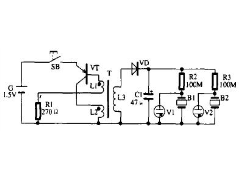

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4874

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499