随着移动电话、WLAN(Wireless Local Area Network)、蓝牙(Bluetooth)的普及化,高频电子设备已经成为生活中的必需品,而电子设备使用的频率也从过去的1GHz逐渐朝5GHz甚至更高频方向发展。由于FET等主动电子组件与电容、电感等被动电子组件性能的提升,使得高频电路的特性获得大幅的改善。以往GHz的电路大多是由micro strip line等分布定数电路所构成,最近因为电子组件芯片化,因此高频电路以集中定数电路居多,不过即使高频电路已经进入集中定数电路时代,然而设计者却还未意识到配线长度、组件形状等分布定数性对高频电路的影响。此外电子组件芯片化之后若单靠是集中定数设计电路,势必会遭遇到设计上的极限,因此必需借助计算机仿真技术,针对pattern与组件的形状、配置(layout)等物理性尺寸进行精密的分析、设计,有鉴于此本文将深入探讨有关5GHz高频电路设计要领。

频率与信号位相

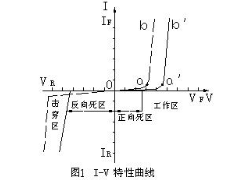

如图1所示5GHz刚好介于C band的中央部位,5GHz的信号在自由空间的波长为60nm,相较之下厚度1.0mm的FR-4玻璃环氧基板上的50Ω micro strip line的波长祇有32 nm,在该line如果组件位置偏差8mm,信号位相会产生900的相违,进而直接、间接造成电路结构、设计以及功能上的差异。此外电子组件芯片化并不代表可以完全取消matching调整等外置组件,换言之设计5GHz等级的高频电路,仍应该以被动电子组件的特性为主要考虑。尤其是使用chip inductor时必需详读该组件的规格表(spec sheet)。表1是太阳诱电公司高频积层chip inductor HK1608系列的型录摘要,值得注意的是表中列示的「自我共振频率」,由于该组件会引发自我共振,所以chip inductor的等价电路会成为电感(inductor)与电容(condenser)的等价电路,当频率低于自我共振频率时,会出现诱导性形成电感(inductor)功能,如果频率高于自我共振频率时就会出现容量性。

图1 频率分布chart

表1 HK1608系列高频积层chip inductor的规格摘要

| 型号 | 电感值(nH) | 最小Q | 最小Q的测试频率 (MHz) | Q的代表值 | 自我共振频率(MHz) | 直流阻抗(Ω) | ||||||

| 测试频率(MHz) | ||||||||||||

| 100 | 300 | 500 | 800 | 1000 | min. | typ. | max. | typ. | ||||

| HK1608 1NOS | 1.0±0.3 | 8 | 100 | 14 | 30 | 40 | 70 | 90 | 10000 | >13000 | 0.05 | 0.015 |

| HK1608 1N2S | 1.0±0.3 | 8 | 100 | 14 | 30 | 40 | 70 | 90 | 10000 | >13000 | 0.05 | 0.015 |

| HK1608 5N6 | 1.0±0.3 | 10 | 100 | 14 | 25 | 33 | 42 | 46 | 4000 | 5800 | 0.18 | 0.09 |

| HK1608 6N8 | 1.0±0.3 | 10 | 100 | 14 | 25 | 33 | 43 | 47 | 4000 | 5600 | 0.22 | 0.11 |

| HK1608 8N2 | 1.0±0.3 | 10 | 100 | 14 | 26 | 34 | 44 | 48 | 3500 | 5200 | 0.24 | 0.13 |

| HK1608R15 | 1.0±0.3 | 8 | 50 | 13 | 19 | 16 | -- | -- | 500 | 800 | 1.2 | 0.73 |

| HK1608R18 | 1.0±0.3 | 8 | 50 | 13 | 18 | 12 | -- | -- | 400 | 700 | 1.3 | 0.85 |

| HK1608R22 | 1.0±0.3 | 8 | 50 | 12 | 16 | -- | -- | -- | 400 | 600 | 1.5 | 0.95 |

图2是忽略阻抗成份单纯的并联共振电路。如果从自我共振频率计算寄生容量时,寄生容量约为0.125pF左右。

图2 chip induct的等价电路

图3是50Ω插入并联(series)与分路(shunt)时的仿真(simulati on)电路。

图3 电感串联与分路的仿真电路

图4与图5分别是并联(series)与分路(shunt)时的通过特性图。为了简化比较因此上述特性图使用祇有电感值(inductance)成份的特性表示,而无寄生容量的特性。由图5可知插入分路(shunt)与祇有电感成份时,两者并无太大差异;相较之下图4的插入并联(series)的场合,会以共振频率为中心出现极大的差异。换言之若将电感当作偏压(bias)电路的扼流圈(choke coil)使用时,寄生容量的影响会比较少,不过若将电感当作matching调整等,亦即所谓的特性调整用途时,寄生容量的影响就会变大。

图4 电感串行电路的通过特性

图5 电感并联电路的通过特性

几乎所有的chip condenser厂商未在产品型录或是数据表(data sheet)记载该组件的自我共振频率,因此必需利用类似MCSIL(Murata Chip S-parameter & Impedance Libra ry)进行chip condenser的等价电路值。图6是MCSIL的画面。

图6 MCSIL的实际画面

虽然chip inductor的等价电路为并联共振电路,不过图7的chip condenser却是串联共振电路。

图7 chip condenser的等价电路

接着利用村田公司MCSIL软件,分析太阳诱电公司1680type GRM18系列GRM1884C1H1R0CZ01高频积层chip inductor的自我共振特性,其结果如下所示:

- 自我共振频率: 5785MHz。

- 阻抗值C: 0.93pF。

- 电感值L: 0.81nH。

图8是50Ω插入并联(series)与分路(shunt)时的仿真(simulation)电路;

图8 电容串联与分路的仿真电路

图9与图10分别是并联(series)与分路(shunt)时的通过特性图。为了简化比较因此用祇有电感值(inductance)成份的特性方式表示,也就是说测试结果并无无寄生容量的特性。由图10的测试结果可知50Ω插入分路(shunt)时,会以共振频率为中心出现极大差异,相较之下50Ω插入并联(series)时,若与祇有电容(capacitor)成份比较,虽然并未出现很大差异,不过在共振频率附近的损失却明显减少。由此可知若将电容单纯当作藕合电容(coup ling condenser)使用时,电感成份的影响会比较少,相较之下或若将电容当作matching特性调整使用时,电感成份的影响则明显增加。

图9 电容串行电路的通过特性

图10 电容并联电路的通过特性

此外GND(Ground)的设计对高频电路具有关键性的影响,如果未正确设计GND,其结果不单是增幅器等主动电路受到影响,经常连filter等被动电路也无法获得预期的性能。以如图11所示的micro strip电路为例,通常多层电路板内侧表层会成为基准的接地层(Ground layer),封装于电路板表层的组件接地,则是利用小直径via hole与内层连接。为了确认与内侧表层连接的表层patter是否属于GND,因此不断变更厚0.8的FR4玻璃环氧基板上的via hole直径,并利用模拟分析探讨via hole的阻抗(impedance)特性,亦即所谓电抗(reactance)特性。

图11 连接表、里层GND的via hole

图12是仿真电路,图13是仿真分析后的阻抗特性。

图12 via hole的simulation电路

图13 via hole的频率阻抗特性

由分析结果可知via hole具有微量的电抗成份,因此多层电路板表面的GND会比照微量的电抗成份,从内侧基准的接地层浮现,如图13所示via hole的直径越大,电抗成份相对的越小。此外频率越高电抗也越大,如果将via hole视为inductor,并计算等价性电感值其结果为:

- 0.067Nh@R=0.5mm

- 基板材质: FR4。

- 基板厚度: 0.8mm。

- 频率: 5GHz。

根据实验结果显示基板厚度越薄,via hole直径越大且复数设置时,基本上可以有效减缓电抗。

-

一款高温报警电路2024年11月13日 81

-

可燃气体全自动点火器2012年09月22日 76

-

LED参数与特性2012年09月18日 118

-

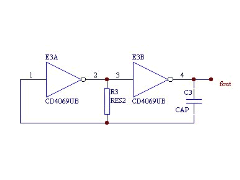

RC振荡电路的几种接法2012年09月10日 221

-

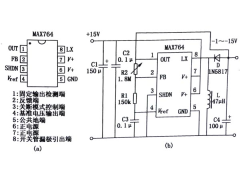

MAX764极性反转电路2012年08月24日 47

-

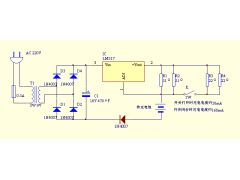

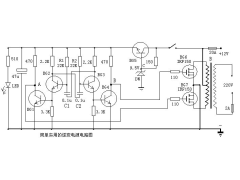

实用恒流充电器2012年08月18日 175

-

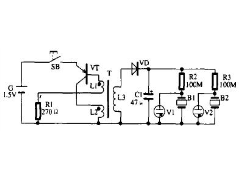

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4874

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

用LM1875替找TDA20302012年09月15日 777

-

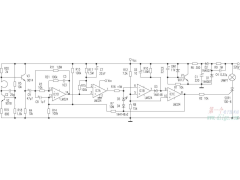

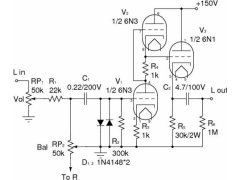

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

1000米晶体稳频FM立体声发射机2012年07月22日 499