这里把仿真单独编号

1) 新建工程

2) 生成原文件

手段CORE Generator Module

Language Templates

3) check syntax

① Behavioral simulate

我觉得从Synthesis and Simulation Design Guide 文件看,应该先RTL Simulation (that is, Behavioral simulate )。其实没

有关系,综合和RTL 仿真的顺序无所谓,这两个不一定要谁在前

己见:注意跑行为仿真前是不需要综合的,仅是RTL 代码仿真

参考:[In-Depth Tutorial] Chapter 4 P91

4) Synthesis

步骤:Entering Constraints (xcf 格式) -> Entering Synthesis Options -> Synthsizing

参考:[In-Depth Tutorial]P43-P50

我觉得这里的constraints 是 synthesis constraints:

《cgd》p18

已见:

参《Xilinx ISE 9.X FPGA/CPLD 设计指南(人民邮电)》P31

综合是把HDL 描述转化为使用基本门电路以及厂家库提供的基本单元进行描述的网表(Netlist)的过程。

综合时需要附加一定的约束,指导综合过程的进行,最常用的约束有管脚位置约束和附加时序约束

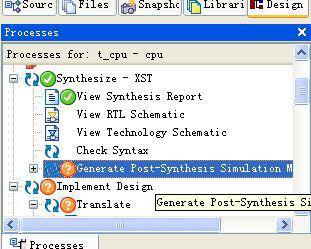

② Post- Synthesis Simulation

这里以《夏宇闻》第17 章的设计为例,前面行为仿真时可以直接仿真cputop 模块(专为仿真写的,不可综合),但在synthesize 时,必须把cpu 模块Set as Top Module,因为cputop 模块是不可综合的,然后点击Generate Post-Synthesis Simulation Model,可以注意到原文件夹下会生成netgen 文件夹,打开会发现有synthsis 文件夹,里面有cpu_synthesis.v文件,这个文件是专门用来仿真的。

但是这里好像无法直接在ISE 中做综合后仿真,然后用MODELSIM,可以建工程,添加顶层测试文件cputop.v 等,然后注意仅需要添加cpu_synthesis.v 文件即可,不需要加cpu.v 及其子文件。

问题注意:

1 原测试文件中cputop.v 中诸如写法“t_cpu.m_alu.opcode”写法现要改成t_cpu.opcode,因为现在模块层次关系被打散了,不再有原模块间关系。

2 在vsim 时要同时选中你的top 层设计和glbl,一起仿真,否则仿真时会出现错误信息“Unresolved reference to 'glbl'”

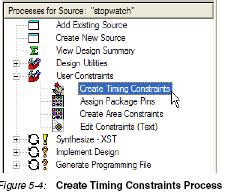

5) (生成分区)、时序约束

Using the Constraints Editor

参考:[In-Depth Tutorial]P116

6) translate the design

输入文件:

输出文件:

作用:把所有的netlist 和design constraint 合并到一起,生成一个ngd 文件供map 工具使用

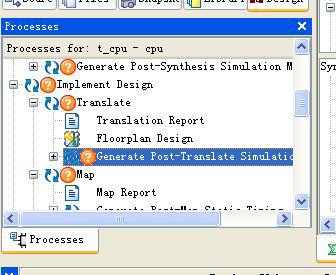

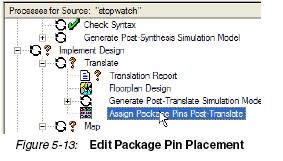

③ Post- Translate Simulation

不点击Generate Post-Translate Simulation Model,则Sources for 中Post-Translate Simulation 是没有内容的。

运行之后文件夹netgen 中会有文件夹translate,其中有文件cpu_translate.v,接下来类似cpu_synthesis.v 方法

7) 管脚分配

工具Floorplan Editor

参考:[In-Depth Tutorial]P120

-

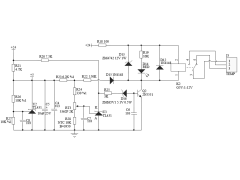

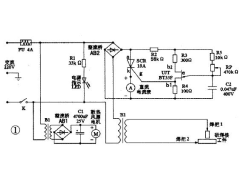

一款高温报警电路2024年11月13日 81

-

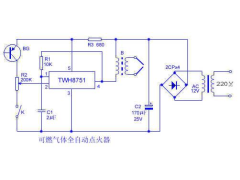

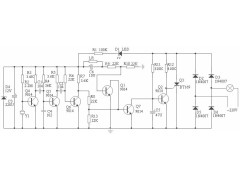

可燃气体全自动点火器2012年09月22日 76

-

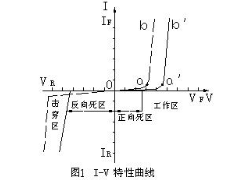

LED参数与特性2012年09月18日 118

-

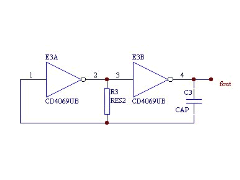

RC振荡电路的几种接法2012年09月10日 221

-

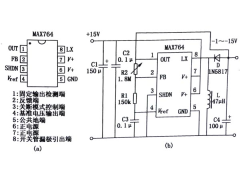

MAX764极性反转电路2012年08月24日 47

-

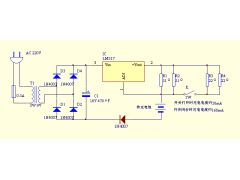

实用恒流充电器2012年08月18日 175

-

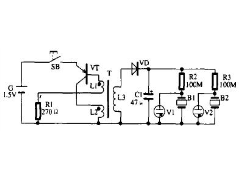

电子催眠器制作2012年08月15日 72

-

多普勒自动电子开关2012年08月02日 78

-

常用物质金属非金属的电阻率、导电率明细表2024年11月23日 4875

-

自制微型交流电焊机2012年07月14日 1143

-

声光控延时开关的制作2024年07月06日 915

-

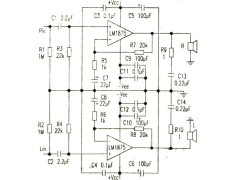

用LM1875替找TDA20302012年09月15日 777

-

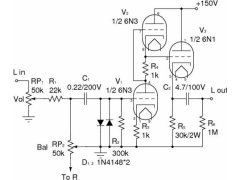

6N3+LM4780功放制作2012年09月13日 653

-

小型太阳能供电板的制作2012年09月08日 649

-

简单的逆变器电路2012年07月08日 560

-

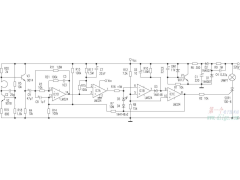

1000米晶体稳频FM立体声发射机2012年07月22日 499