基于FPGA 的高阶全数字锁相环的设计与实现

2012-06-02

单长虹 王彦 陈文光 陈忠泽

6

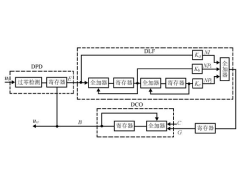

摘要:提出了一种实现高阶全数字锁相环的新方法。该锁相环以数字比例积分控制取代了传统的一些数字环路滤波控制方法,具有电路结构简单、控制灵活、跟踪精度高、环路性能好和易于集成的特点。文中介绍了该高阶全数字锁相环的系统结构和工作原理,对其性能进行了理论分析和计算机仿真。应用EDA 技术设计了该系统,并用FPGA实 ..

[查看全文]

固定几何结构的FFT算法及其FPGA实现

2012-06-02

11

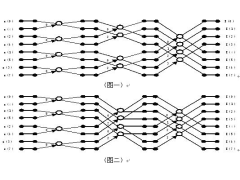

1.引言 DFT及其快速算法FFT是信号处理领域的核心组成部分。FFT算法多种多样,按数据组合方式不同一般分时域和频域,按数据抽取方式的不同又可分为基2,基4等。各算法的优缺点视不同的制约因素而不同。FFT的实现方法也多种多样,可以用软件实现,也可以用硬件实现,用软件在PC机或工作站上实现则计算速度很慢。一般多结合 ..

[查看全文]

基于FPGA的多路脉冲重复频率跟踪器

2012-06-02

12

摘要:在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟踪器,它解决了在密集信号环境下信号跟踪的实时性问题,减小了系统体积。经过实验验证,其各项指标均达到了设计要求。 随着高科技的迅速发展,现代战争已经不仅是传统意义战场上 ..

[查看全文]

FPGA三国志-第一篇/不可不看的故事

2012-06-02

wisdomz

6

CPLD的时代 我在12年前,偶然接触PLD,没有想到自己居然就在这个行当里安身下来。可是这个行业也的确是个飞速发展的行业,十多年过去后,从当初的接近十家主要供应商,到今天已经激烈搏杀后,只有差不多如论坛题目一样的,成为了今天三足鼎立的局面。想来想去,决定以这个名字作为论坛的主题。同时也和大家分享我多年来的一 ..

[查看全文]

静态时序分析在高速FPGA设计中的应用

2012-06-02

周海斌

28

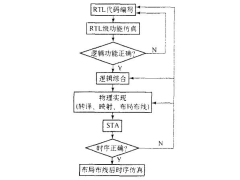

摘要:介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进时序收敛的方法。结合设计实例,阐明了STA在高速、大规模FPGA开发中的应用。实践表明,随着数字设计复杂度的增加,在后端的时序验证环节,与传统的动 ..

[查看全文]

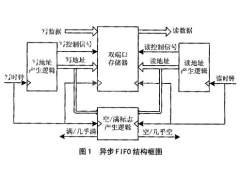

异步FIFO结构及FPGA设计

2012-06-02

7

摘要 :首先介绍异步FIFO的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法;在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA实现。 1、异步FIFO介绍 在现代的集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟。多时钟域带来的一个问题就是,如何设计异步时钟之间的接口 ..

[查看全文]

Xilinx公司FPGA设计技术问答

2012-06-02

7

问:我在ISE4.1中,用fpga express verilog编译的某些文件,用modelsimxe只能前仿,不能后仿,不知5.1i是否有改进? 答: 4.1i支持用Modelsim XE实现行为级仿真和时间仿真,5.1I也同样。请用热线(china_support xilinx.com)打开一个例子并在4.1i/Modelsim XE运行时间仿真以解决你的问题。 问:和5.1结合比较好的验证工具 ..

[查看全文]

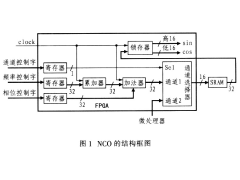

基于FPGA和SRAM的数控振荡器的设计与实现

2012-06-02

佟力永 肖山竹

10

1 、引言 数控振荡器是数字通讯中调制解调单元必不可少的部分,同时也是各种数字频率合成器和数字信号发生器的核心。随着数字通信技术的发展,对传送数据的精度和速率要求越来越高。如何得到可数控的高精度的高频载波信号是实现高速数字通信系统必须解决的问题,可编程逻辑器件和大容量存储器的发展为这一问题的解决带来了曙光 ..

[查看全文]

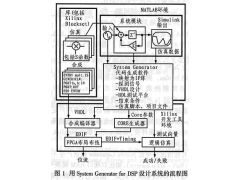

在Matlab中实现FPGA硬件设计

2012-06-02

江 霞

36

摘要 :System Generator for DSP是Xilinx公司开发的基于Matlab的DSP开发工具?熗?时也是一个基于FPGA的信号处理建模和设计工具。文章介绍了在Matlab中使用System Generator for DSP实现FPGA硬件设计的方法,同时给出了一个应用实例。 关键词 :Matlab;FPGA;System Generator;DSP 近年来,在数字通信、网络、视 ..

[查看全文]

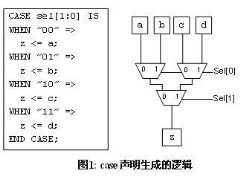

复用器重构降低FPGA成本

2012-06-02

12

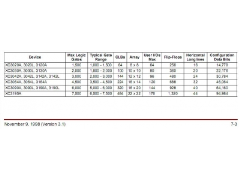

摘要 本文介绍了一种新的能够降低FPGA实际设计20%成本的综合算法。该算法通过减少复用器所需查找表(LUT)的数量来实现。算法以效率更高的4:1复用器替代2:1复用器树。算法性能关键在于寻找总线上出现的复用器数量。新的优化方法占用一定的逻辑,这些逻辑由总线进行分担,从而减少了总线上每个比特位所需的逻辑。 1.引言 复 ..

[查看全文]

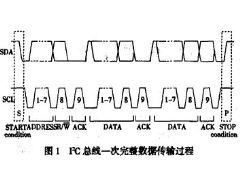

FPGA有限状态机模拟I2C总线设计

2012-06-02

潘小冬

18

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模 ..

[查看全文]

CPLD开发板和FPGA开发板的区别

2012-06-02

抽烟的鱼

19

市面上尤其是学校里面可以看到Xilinx公司或者Altera公司各种不同的开发板,其实只有两个大类,CPLD开发板和FPGA开发板。尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点: ①CPLD更适合完成各种组合逻辑,FPGA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富 ..

[查看全文]

推荐文章

最新文章

热门文章