Verilog讨论组精彩内容摘录

2013-03-31

12

问题:我遇到了一个问题,希望能得到帮助。 我在用FPGA(ALTERA 10K30)做仿真实验时,内部的计数器总是计数不正常,但是我在微机中用ModelSim仿真的结果是正确的,所以逻辑应该没有问题,问题出在FPGA,请教各位,我该如何解决这个问题。谢谢! I met a question,hope someone could do me a favor. when I used FPGA ..

[查看全文]

全数字锁相环的verilog源代码

2013-03-28

15

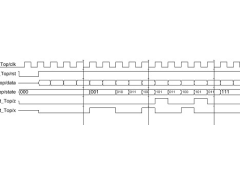

仿真已通过 module dpll(reset,clk,signal_in,signal_out,syn); parameter para_K=4; parameter para_N=16; input reset; input clk; input signal_in; output signal_out; output syn; reg signal_out; reg dpout; reg delclk; reg addclk; reg add_del_clkout; reg [7:0]up_down_cnt; reg [2:0]cnt8; reg [8:0]cnt_N; reg syn; reg ..

[查看全文]

Verilog HDL设计练习进阶(八)

2013-03-28

9

练习八. 利用有限状态机进行复杂时序逻辑的设计 目的:掌握利用有限状态机实现复杂时序逻辑的方法; 在数字电路中我们已经学习过通过建立有限状态机来进行数字逻辑的设计,而在Verilog HDL硬件描述语言中,这种设计方法得到进一步的发展。通过Verilog HDL提供的语句,我们可以直观地设计出适合更为复杂的时序逻辑的电路。关于 ..

[查看全文]

Verilog学习笔记

2013-03-16

9

一般认为 Verilog HDL在系统级抽象方面比VHDL略差一些,而在门级开关电路描述方面比VHDL要强的多 写了第一个verilog程序,是一个加法器内容如下 module adder(count,sum,a,b,cin); input[2:0] a,b; input cin; output count; output [2:0] sum; assign{count,sum}=a+b+cin; endmodule 开始编译出现了几次错误,后来发现给实体 ..

[查看全文]

Verilog模拟PS2协议

2013-03-14

13

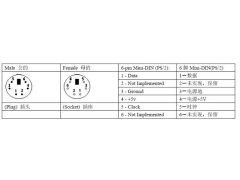

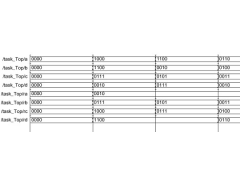

本来以为模拟PS2协议相当的麻烦,今天下了一本PS2协议手册看了半天,原来读键盘值相当简单嘛,比模拟SPI、I2C简单多了呵呵。 下面介绍一下具体过程 1.明确接线关系,只需接4根线,VCC要+5V,3.3我测试过不能用,时钟和数据线要用bidir双向口线,FPGA可以不用外接上拉电阻。另外,USB键盘也可以用,只要用一个转接头转成 ..

[查看全文]

一个好用的Verilog串口UART程序

2013-03-12

16

出自http://www.asic-world.com/,测试过了很好用。==========================================================================//----------------------------------------------------- // Design Name : uart // File Name: uart.v // Function: Simple UART // Coder: Deepak Kumar Tala //------- ..

[查看全文]

Verilog串口通讯设计

2013-03-11

11

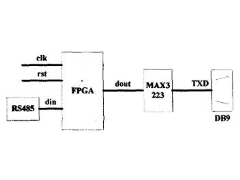

1 串口通信基本特点 随着多微机系统的应用和微机网络的发展,通信功能越来越显得重要。串行通信是在一根传输线上一位一位地传送信息.这根线既作数据线又作联络线。串行通信作为一种主要的通信方式,由于所用的传输线少,并且可以借助现存的电话网进行信息传送,因此特别适合于远距离传送。在串行传输中,通信双方都按通信协议 ..

[查看全文]

八位的伪随机数产生的verilog源程序

2013-03-11

11

linear-feedback-shift-register 下面是一个八位的伪随机数产生的verilog文件,我想够用了。 // DEFINES `timescale 1ns/1ns `define DEL1// Clock-to-output delay. Zero // time delays can be confusing // and sometimes cause problems. // These are good tap values for 2 to 32 bits `define TAP22'b11 `define TAP33' ..

[查看全文]

Verilog-HDL的基本概念

2013-03-09

常晓明

13

Verilog-HDL与CPLD/FPGA设计应用讲座 第 3 讲 Verilog-HDL的基本概念 3.1 与门的描述 3.2 与非门的描述 3.3 非门的描述 3.4 或门的描述 3.5 或非门的描述 3.6 缓冲器的描述 3.7 逻辑仿真与测试模块 3.1 与门的描述 让我们通过最简单的例子来认识一下Verilog-HDL的基本用法。 (1)模块的定义 用Verilog-HDL做数字电路描述,一开始所 ..

[查看全文]

用verilog编写的多功能数字钟

2013-02-08

8

/* 信号定义: clk: 标准时钟信号,本例中,其频率为4Hz; clk_1k: 产生闹铃音、报时音的时钟信号,本例中其频率为1024Hz; mode: 功能控制信号; 为0:计时功能; 为1:闹钟功能; 为2:手动校时功能; turn: 接按键,在手动校时功能时,选择是调整小时,还是分钟; 若长时间按住该键,还可使秒信号清零,用于精确调时; chan ..

[查看全文]

Verilog HDL设计练习进阶(七)

2013-01-26

10

练习七. 在Verilog HDL中使用任务(task) 目的:掌握任务在结构化Verilog HDL设计中的应用。 仅有函数并不能完全满足Veirlog HDL中的运算需求。当我们希望能够将一些信号进行运算并输出多个结果时,采用函数结构就显得非常不方便,而任务结构在这方面的优势则十分突出。任务本身并不返回计算值,但是它通过类似C语言中形参与 ..

[查看全文]

Verilog HDL常见问题

2013-01-19

4

问题:在使用case语句建模组合逻辑的时候,综合工具提示会出现latch 原因:产生这个错误时候可以从下面三个方面检查: 1. 看看这个语句块的敏感列表是否完备,也就是是否所有的“输入”信号都位于敏感列表内; 2. case语句是否覆盖了所有可能的条件; 3. “输出”信号是否在每个分支上都进行了赋值操作; 例 ..

[查看全文]

推荐文章

最新文章

热门文章