从FPGA或PLD转换到门阵列

2013-04-02

6

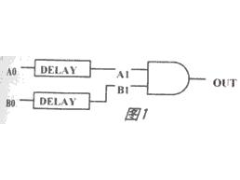

概述 从FPGA或PLD转换到门阵列是经济高效的,有时甚至只需几百个单元就能实现。这已经引起越来越多设计者提出同样的问题:这种转换设计需要什么后续技术?事实上转换到门阵列面临着许多电路的时序问题,这在FPGA设计中是不被注意的。 本文论述了转换时遇到的几种由于设计不当所造成的时序问题,提出了避免这些问题的方案。 ..

[查看全文]

基于CPLD的DSP人机接口模块设计

2013-03-21

冯志强

12

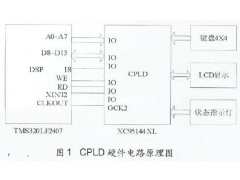

CPLD(Complex programmable Logic Device,复杂可编程逻辑器件)是在传统的PAL、GAL基础上发展而来的,具有多种工作方式和高集成、高速、高可靠性等明显的特点。在超高速领域和实时测控方面有非常广泛的应用,日前的CPLD普遍基于E2PROM和Flash电可擦除技术,可实现100次以上擦写循环。 CPLD选择及其扩展模块的设计 由 ..

[查看全文]

基于CPLD 器件的单稳态脉冲展宽电路

2013-03-18

袁绍明

20

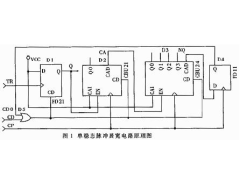

摘要:具体介绍了基于CPLD 器件设计单稳态窄脉冲展宽电路的详细过程和这种单稳态窄脉冲展电路的特点,给出了相应的时序仿真波形,提出了提高展宽脉冲宽度精确度的方法。 关键词:CPLD 器件 单稳态 脉冲信号 时序仿真 在数字电路设计中,当需要将一输入的窄脉冲信号展宽成具有一定宽度和精度的宽脉冲信号时,往往很快就想到利用 ..

[查看全文]

CPLD与51单片机总线接口

2013-03-12

37

前段时间做的CPLD与51单片机总线接口`timescale 1ns/1ns module IO_KZ(Data,P27,WR,RD,ALE,CLR,OUTKEY,OUT30,CS,CS1,LEDCS,OC); inout [7:0]Data; input WR; input P27; input RD; input ALE; input CLR; input OC; input [4:0]OUTKEY; output [59:0]OUT30; output [1:0]CS; output CS1; output [14:0]LEDCS ..

[查看全文]

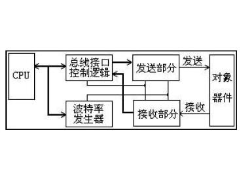

在CPLD管理下实现高效多串口中断源

2013-03-06

18

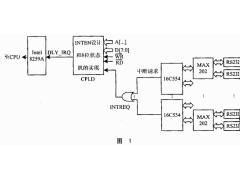

近几年来,随着后PC时代的来临,具有简洁、高效等特点的嵌入式系统得到了飞速的发展。嵌入式技术发展到今天已将各种计算机技术多层次、多方面的交叉融合在了一起。嵌入式系统加快了工业设计进程,降低了开发成本及其风险,使用简便,扩展灵活,高效精简,可方便地应用于各工业领域。中断请求采用边沿触发来进行中断检测,通 ..

[查看全文]

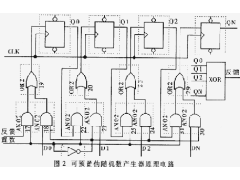

伪随机序列及PLD实现在程序和系统加密中的应用

2013-03-01

11

摘 要 : 讨论了用伪随机序列实现程序加密保护及其可编程逻辑器件实现的原理、方法和具体操作,给出了在微机软件和单片机/DSP系统中程序加密的实际运用举例。 可编程逻辑器件(PLD)经历了PAL、GAL、CPLD 和FPGA几个发展阶段。使用PLD具有设计灵活、调试方便、系统可靠性高等众多优点,并有利于硬件设计的保护,防止他人 ..

[查看全文]

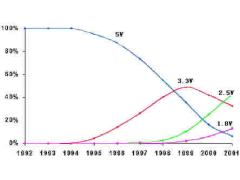

低电压PLD/FPGA的供电设计

2013-02-11

13

由于半导体制造工艺的原因,低电压器件的成本比传统5V器件更低,性能更优,加上多数器件的I/O脚可以兼容5v/3.3v TTL电平,可以直接使用在原有系统中,所以各大半导体公司都将3.3v,2.5v等低电压集成电路作为推广重点,如高端的DSP,PLD/FPGA产品已广泛采用3.3v,2.5v甚至1.8v,1.5v供电。 面对低电压芯片的广泛使用,我 ..

[查看全文]

低电压CPLD EPM7512A的混合电压系统设计

2013-02-09

8

摘要:较详细地阐述不同逻辑电平的接口原理。以低压CPLD EPM7512A为例,给出在混合电压系统中的具体设计方案。 引 言 随着微电子技术的飞速发展,体积更小、功耗更低、性能更佳的低压芯片不断涌现。I/O电平逻辑向3.3V、 2.5V、1.8V,甚至更低的方向发展。但数十年来,由于5V电源的器件一直占据比较重要的市场,在系统设计 ..

[查看全文]

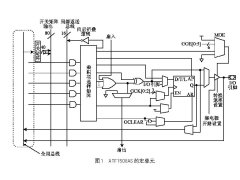

基于CPLD的串并转换和高速USB通信设计

2013-02-03

王朔 李刚 于学敏

13

摘要:CPLD可编程技术具有功能集成度高、设计灵活、开发周期短、成本低等特点。介绍基于ATMEL 公司的CPLD芯片ATF1508AS设计的串并转换和高速USB及其在高速高精度数据采集系统中的应用。 可编程逻辑器件(PLD)是20世纪70年代在ASIC设计的基础上发展起来的一种划时代的新型逻辑器件。自PLD器件问世以来,制造工艺上 ..

[查看全文]

用MAX+PLUSⅡ开发Altera CPLD

2013-02-01

邹于丰

10

【摘 要】 介绍利用MAX+PLUSⅡ软件对Altera公司的CPLD进行图形设计、编译以及在系统编程的基本方法和步骤。 【关键词】 MAX+PLUSⅡ软件,CPLD,在线编程 1 引 言 Altera公司是世界三大CPLD/FPGA厂家之一,它的器件能达到最高的性能和集成度,不仅仅因为采用了先进的工艺和全新的逻辑结构,还在于它提供了现代化的 ..

[查看全文]

cpld与PC机通讯vhdl代码

2013-01-23

10

--功能:实现cpld与pc机通讯 --原理:模拟232的发送时序每次发送10bits,一个开始位,八个数据位,一个停止位. --波特率:9600bps --环境:cpld器件:epm7128stc100-10,外部1m 时钟,pc机端:串口调试助手. --操作:从串口调试助手中发送一个byte.cpld接收到信号再返回到串口调试助手. --本程序仅供学习,不得用与商业. --作者:sages ..

[查看全文]

基于FPGA/CPLD设计与实现UART(VHDL)

2013-01-20

24

1 引言 由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA/CPLD和嵌入系统的多种模式。可以说EDA产业已经成为电子信息类产品的支柱产业。EDA之所以能蓬勃发展的关键因素之一就是采用了硬件描述语言(H ..

[查看全文]

推荐文章

最新文章

热门文章