高速电子线路的信号完整性设计(一)

2012-11-16

于波

24

1、引言 当今电子技术的发展日新月异,大规模超大规模集成电路越来越多地应用到通用系统中。同时,深亚微米工艺在IC设计中的使用,使得芯片的集成规模更大。从电子行业的发展来看,1992年只有40%的电子系统工作在30MHz以上的频率,而且器件多数使用DIP、PLCC等体积大、管脚少的封装形式,到1994年已有50%的设计达到了5 ..

[查看全文]

高速电子线路的信号完整性设计(三)

2012-06-29

于波

19

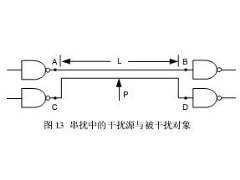

5、串扰分析 当今飞速发展的电子设计领域,高速化和小型化已经成为一种趋势。如何在缩小电子系统体积的同时,保持并提高系统的速度与性能成为摆在设计者面前的一个重要课题。信号频率变高,边沿变陡,印刷电路板的尺寸变小,布线密度加大等都使得串扰越来越成为一个值得注意的问题。而随着电子工程师不断把设计推向技术与工艺 ..

[查看全文]

高速电子线路的信号完整性设计(二)

2012-06-02

于波

13

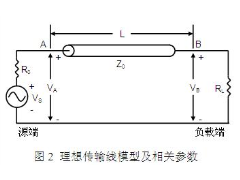

4、信号发射与端接技术 4.1、 信号反射的形成 传输线上的阻抗不连续会导致信号反射,我们以图2所示的理想传输线模型来分析与信号反射有关的重要参数。图中,理想传输线L被内阻为R0的数字信号驱动源VS驱动,传输线的特性阻抗为Z0,负载阻抗为RL。 理想的情况是当R0=Z0=RL时,传输线的阻抗是连续的,不会发生任何反射,能 ..

[查看全文]

推荐文章

最新文章

热门文章